Reference Manual ADuCM356

REGISTER DETAILS: DIGITAL DIE WAKE-UP TIMER

analog.com Rev. A | 301 of 312

ALARM 2 REGISTER

Address: 0x40001444, Reset: 0x0000, Name: ALM2

ALM2 specifies the fractional nonprescaled bits of the WUT alarm target time value, down to an individual 32 kHz clock cycle, where the overall

alarm is defined as ALM1, ALM0, and ALM2.

The number of valid bits that can legitimately have values of one optionally written to them in ALM2 equals the number of prescale bits specified

by the PRESCALE2EXP bit field of the CR1 MMR. If a bit position in ALM2 is set to one, such that this is incompatible with PRESCALE2EXP,

the whole value of ALM2 is treated by the WUT as if it were zero.

Any write to ALM2 pends until corresponding writes to ALM0 and ALM1 are carried out by the CPU, so that the combined 47-bit alarm

redefinition can be executed as a single transaction. ALM0, ALM1, and ALM2 can be written in any order, but coordinated, triple writes must be

carried out by the CPU to have any effect on the WUT alarm. ALM2 can be written to regardless of whether ALMEN or CNTEN is active in the

CR0 register.

In contrast, on RTC1, full support for the fractional alarm time is present, such that an alarm can be specified down to an individual 32 kHz clock

cycle using ALM2.

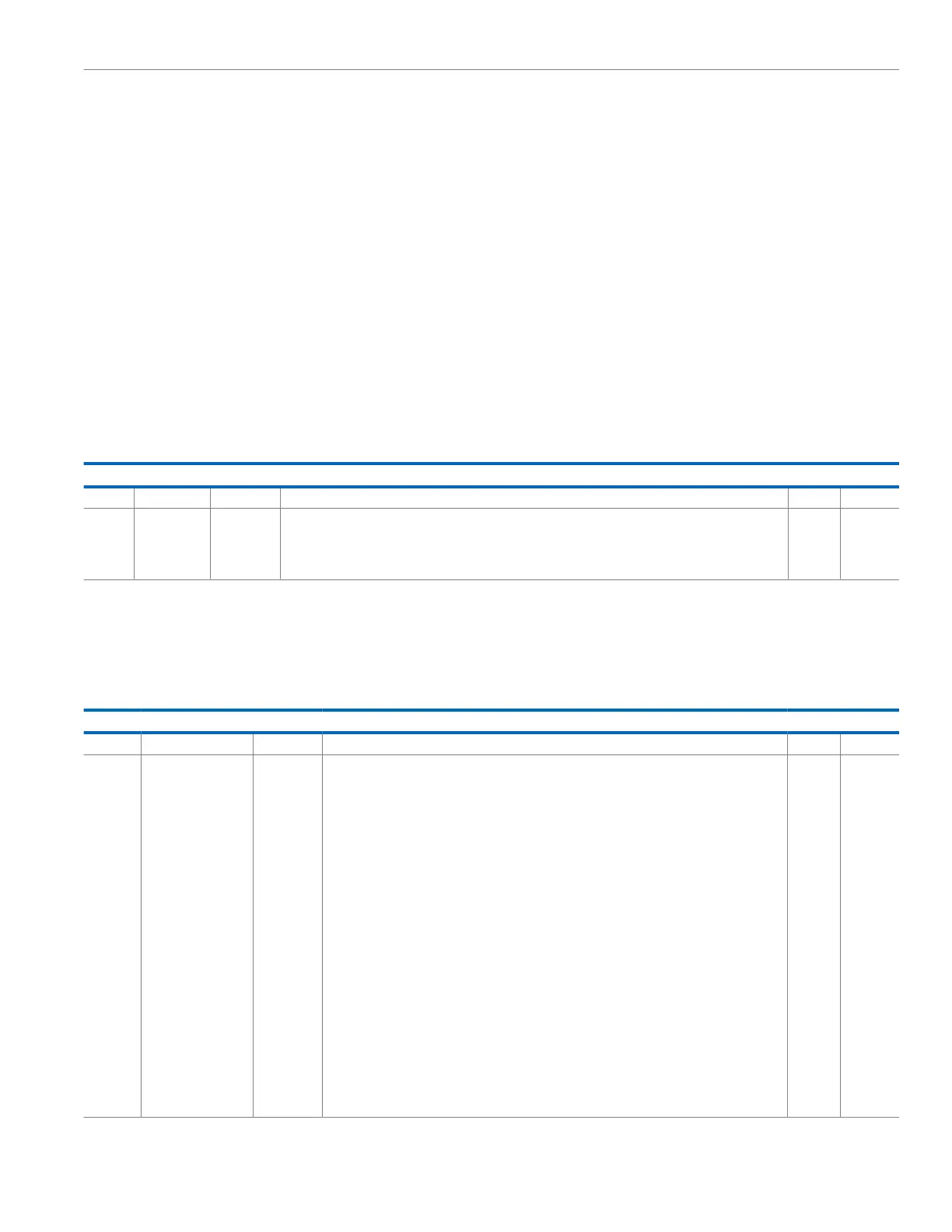

Table 395. Bit Descriptions for ALM2

Bits Bit Name Settings Description Reset Access

15 Reserved Reserved. 0x0 R

[14:0] VALUE Fractional Nonprescaled Bits of the WUT Alarm Target Time. Note that any value written to ALM2 must be

in keeping with the number of prescale bits specified by the PRESCALE2EXP field of the CR1 MMR. If a

value in ALM2 cannot be reached by the degree of prescaling configured by PRESCALE2EXP, the whole

value of ALM2 is treated as if it were zero.

0x0 R/W

STATUS 6 REGISTER

Address: 0x40001488, Reset: 0x7900, Name: SR6

SR6 is a status register that provides the unread status of snapshots of input capture channels, SNAP0, SNAP1, and SNAP2.

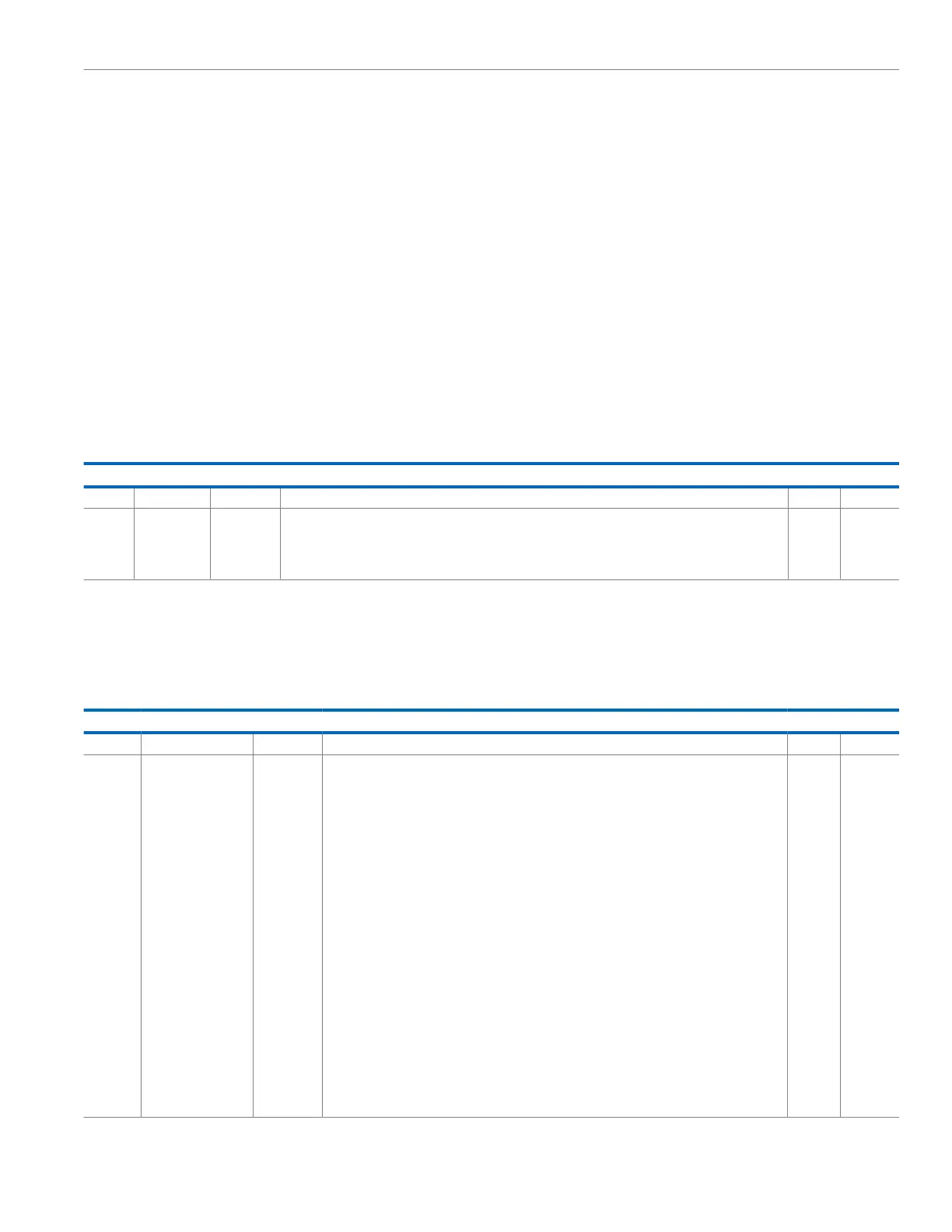

Table 396. Bit Descriptions for SR6

Bits Bit Name Settings Description Reset Access

[15:11] Reserved Reserved. 0xF R

[10:9] RTCFRZCNTPTR Pointer for the Triple Read Sequence of the CNTx MMRs. This bit indicates the sequence number

for the next read in triple read sequences of the CNTx registers. CNTx allows a coherent triple

16-bit read of the 47-bit WUT count contained in CNT2, CNT1, and CNT0. CNTx is always read

in sequences of three reads (although these can be spread out in time, or have other APB

accesses interspersed), so that the first read in the sequence returns the current value of CNT0.

Simultaneously with this first read, a snapshot is taken of the values of CNT2 and CNT1 so that

in the second and third reads in the sequence of CNTx, the snapshot values of CNT1 and CNT2

are returned, respectively. In this way, a triple read of CNTx gives an overall 47 bits of the WUT

count that belong together and are coherent with each other, even though the actual continuing

value of CNT2, CNT1, and CNT0 keeps advancing while the WUT counts real time. This bit

both indicates the sequence number in the triple read and acts a read data select for the value

returned when CNTx is read. Normally, this bit keeps advancing by one, starting from 0b00, and

wrapping from 0b10 to 0b00 with every read. However, to clear the CNTx pointer and reinitialize

the count sequence for reads of CNTx, the CPU can write a software key (value of 0x9376) to the

GWY register.

0x0 R

00 The next read of CNTx causes the read data for CNTx to be the current value of CNT0 and takes

a coherent snapshot of the current values of CNT2 and CNT1 for return during the subsequent

two reads of CNTx. The value that can be read in SNAP0, SNAP1, and SNAP2 is due to a

software initiated snapshot.

01 The next read of CNTx is the second in a triple read sequence and returns the snapshot of CNT1

that was taken when the first read of CNTx in the sequence occurred.

Loading...

Loading...