Reference Manual ADuCM356

REGISTER DETAILS: PROGRAMMABLE SWITCHES

analog.com Rev. A | 122 of 312

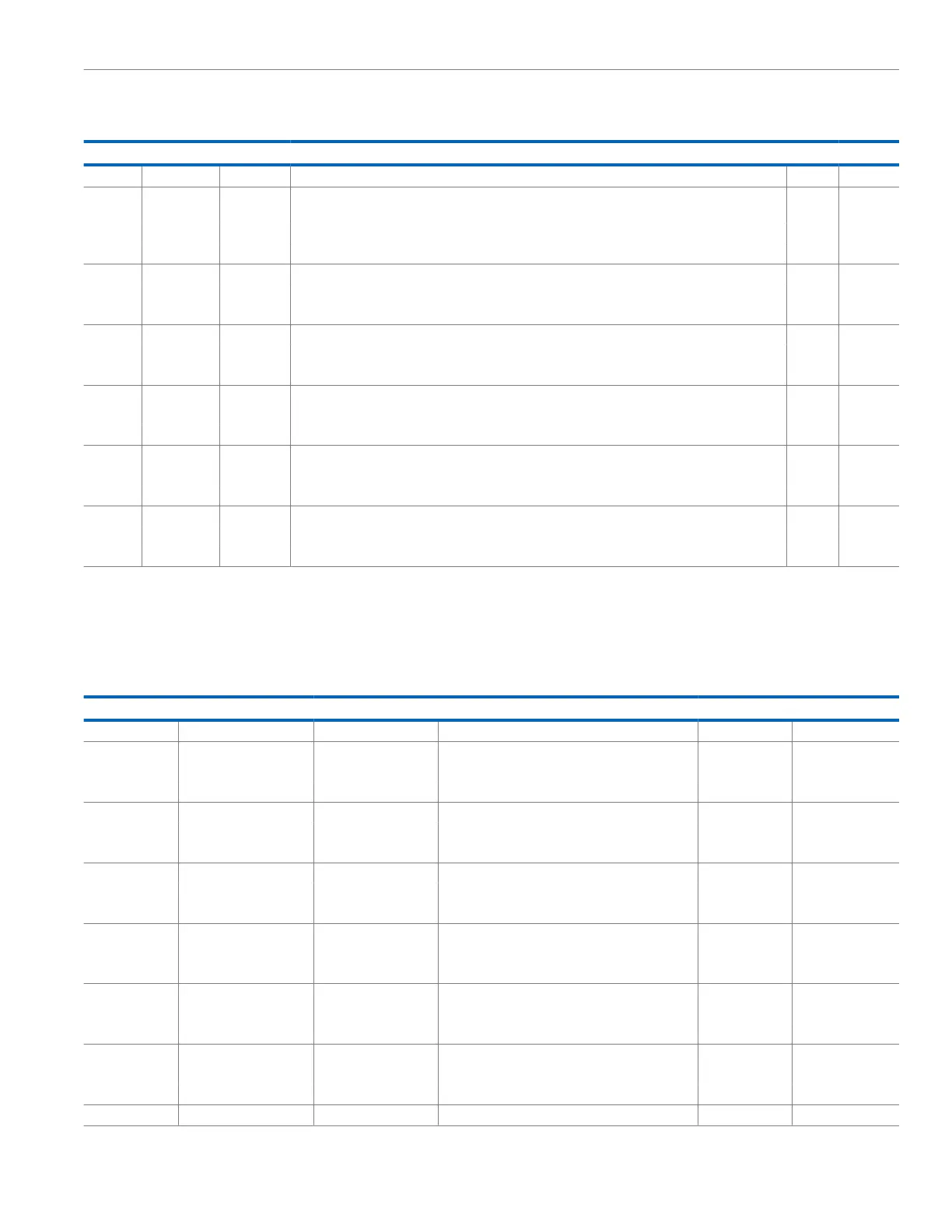

Table 148. Bit Descriptions for TSWFULLCON (Continued)

Bits Bit Name Settings Description Reset Access

1 Switch closed.

5 T6 Control of T6 Switch. Allows connection of the R

CAL

path on to the DE0 input to calibrate the R

LOAD03

and R

TIA2_03

resistors.

0x0 R/W

0 Switch open.

1 Switch closed.

4 T5 Control of T5 Switch. Connects high-speed TIA inverting input to the SE0 pin via T9 and R

LOAD02

. 0x0 R/W

0 Switch open.

1 Switch closed.

3 T4 Control of T4 Switch. Connects high-speed TIA inverting input to the AIN3/BUF_VREF1V8 pin via T9. 0x0 R/W

0 Switch open.

1 Switch closed.

2 T3 Control of T3 Switch. Connects high-speed TIA inverting input to the AIN2 pin via T9. 0x0 R/W

0 Switch open.

1 Switch closed.

1 T2 Control of T2 Switch. Connects high-speed TIA inverting input to the AIN1 pin via T9. 0x0 R/W

0 Switch open.

1 Switch closed.

0 T1 Control of T1 Switch. Connects high-speed TIA inverting input to the AIN0 pin via T9. 0x0 R/W

0 Switch open.

1 Switch closed.

DX SWITCH MATRIX STATUS REGISTER

Address: 0x400C21B0, Reset: 0x00000000, Name: DSWSTA

This gives the status of the Dx switches shown in Figure 27.

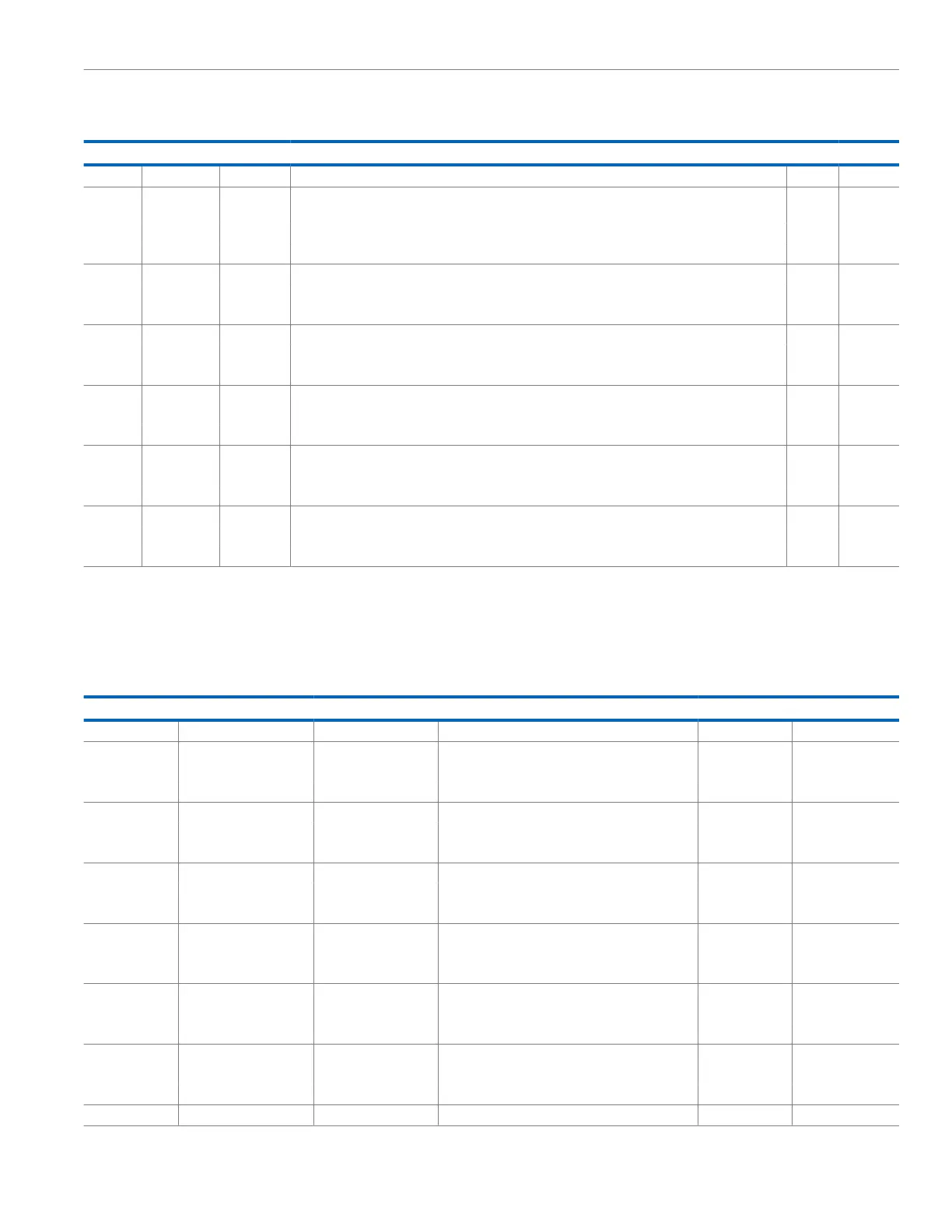

Table 149. Bit Descriptions for DSWSTA

Bits Bit Name Settings Description Reset Access

[31:8] Reserved Reserved. 0x0 R

7 D8STA Status of D8 Switch. 0x0 R

0 Switch open.

1 Switch closed.

6 D7STA Status of D7 Switch. 0x0 R

0 Switch open.

1 Switch closed.

5 D6STA Status of D6 Switch. 0x0 R

0 Switch open.

1 Switch closed.

4 D5STA Status of D5 Switch. 0x0 R

0 Switch open.

1 Switch closed.

3 D4STA Status of D4 Switch. 0x0 R

0 Switch open.

1 Switch closed.

2 D3STA Status of D3 Switch. 0x0 R

0 Switch open.

1 Switch closed.

1 D2STA Status of D2 Switch. 0x0 R

Loading...

Loading...