Reference Manual ADuCM356

REGISTER DETAILS: I

2

C

analog.com Rev. A | 228 of 312

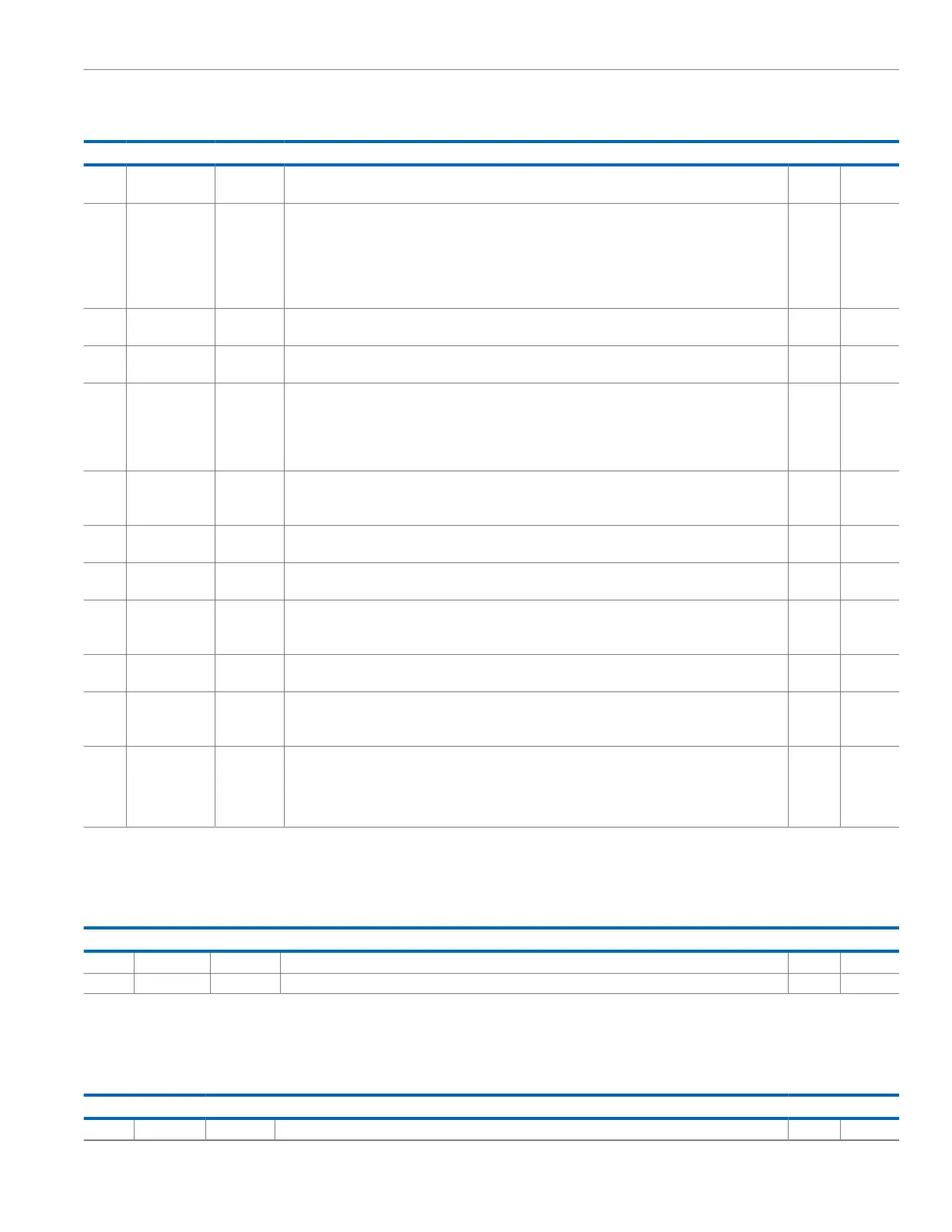

Table 284. Bit Descriptions for MSTAT (Continued)

Bits Bit Name Settings Description Reset Access

12 MTXUNDR Initiator Transmit Underflow. Asserts when the I

2

C initiator ends the transaction due to the transmit FIFO

being empty. This bit is asserted only when MCTL, Bit 5 is set.

0x0 RC

11 MSTOP Stop Driven by this I

2

C Initiator. Asserts when this I

2

C initiator drives a stop condition on the I

2

C bus. This

bit, when asserted, can indicate a transaction completion, transmit underflow, receive overflow, or a no

acknowledge by the target. This bit is different from the TCOMP bit because this bit is not asserted when

the stop condition occurs due to any other I

2

C initiator. No interrupt is generated for the assertion of this

bit. However, if MCTL, Bit 8 is 1, every stop condition generates an interrupt and this bit can be read.

When this bit is read, it clears status.

0x0 RC

10 LINEBUSY Line is Busy. Asserts when a start is detected on the I

2

C bus. Deasserts when a stop is detected on the

I

2

C bus.

0x0 R

9 MRXOVR Initiator Receive FIFO Overflow. Asserts when a byte is written to the receive FIFO when the FIFO is

already full. When the bit is read, it clears the status.

0x0 RC

8 TCOMP Transaction Complete or Stop Detected. Transaction complete. This bit asserts when a stop condition is

detected on the I

2

C bus. If MCTL, Bit 8 is 1, an interrupt is generated when this bit asserts. This bit only

asserts if the initiator is enabled (MCTL, Bit 0 = 1). Use this bit to determine when it is safe to disable the

initiator. This bit can also be used to wait for another initiator transaction to complete on the I

2

C bus when

this initiator loses arbitration. When this bit is read, it clears status. This bit can drive an interrupt.

0x0 RC

7 NACKDATA Acknowledge Not Received in Response to Data Write. This bit asserts when an acknowledge is not

received in response to a data write transfer. If MCTL, Bit 7 is 1, an interrupt is generated when this bit

asserts. This bit can drive an interrupt. This bit is cleared on a read of the MSTAT register.

0x0 RC

6 MBUSY Initiator Busy. This bit indicates that the initiator state machine is servicing a transaction. It is cleared if the

state machine is idle or another device has control of the I

2

C bus.

0x0 R

5 ALOST Arbitration Lost. This bit asserts if the initiator loses arbitration. If MCLT, Bit 6 is 1, an interrupt is generated

when this bit asserts. This bit is cleared on a read of the MSTAT register. This bit can drive an interrupt.

0x0 RC

4 NACKADDR Acknowledge Not Received in Response to an Address. This bit asserts if an acknowledge is not received

in response to an address. If MCTL, Bit 7 is 1, an interrupt is generated when this bit asserts. This bit is

cleared on a read of the MSTAT register. This bit can drive an interrupt.

0x0 RC

3 MRXREQ Initiator Receive Request. This bit asserts when there is data in the receive FIFO. If MCTL, Bit 4 is 1, an

interrupt is generated when this bit asserts. This bit can drive an interrupt.

0x0 R

2 MTXREQ Initiator Transmit Request. This bit asserts when the direction bit is 0 and the transmit FIFO is either

empty or not full. If MCTL, Bit 5 is 1, an interrupt is generated when this bit asserts. This bit can drive an

interrupt.

0x0 R

[1:0] MTXF Initiator Transmit FIFO Status. Shows the initiator transmit FIFO status. 0x0 R

00 FIFO empty.

10 1 byte in FIFO.

11 FIFO full.

INITIATOR RECEIVE DATA REGISTER

Address: 0x40003008, Reset: 0x0000, Name: MRX

Table 285. Bit Descriptions for MRX

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] VALUE Initiator Receive. Allows access to the receive data FIFO. The FIFO can hold two bytes. 0x0 R

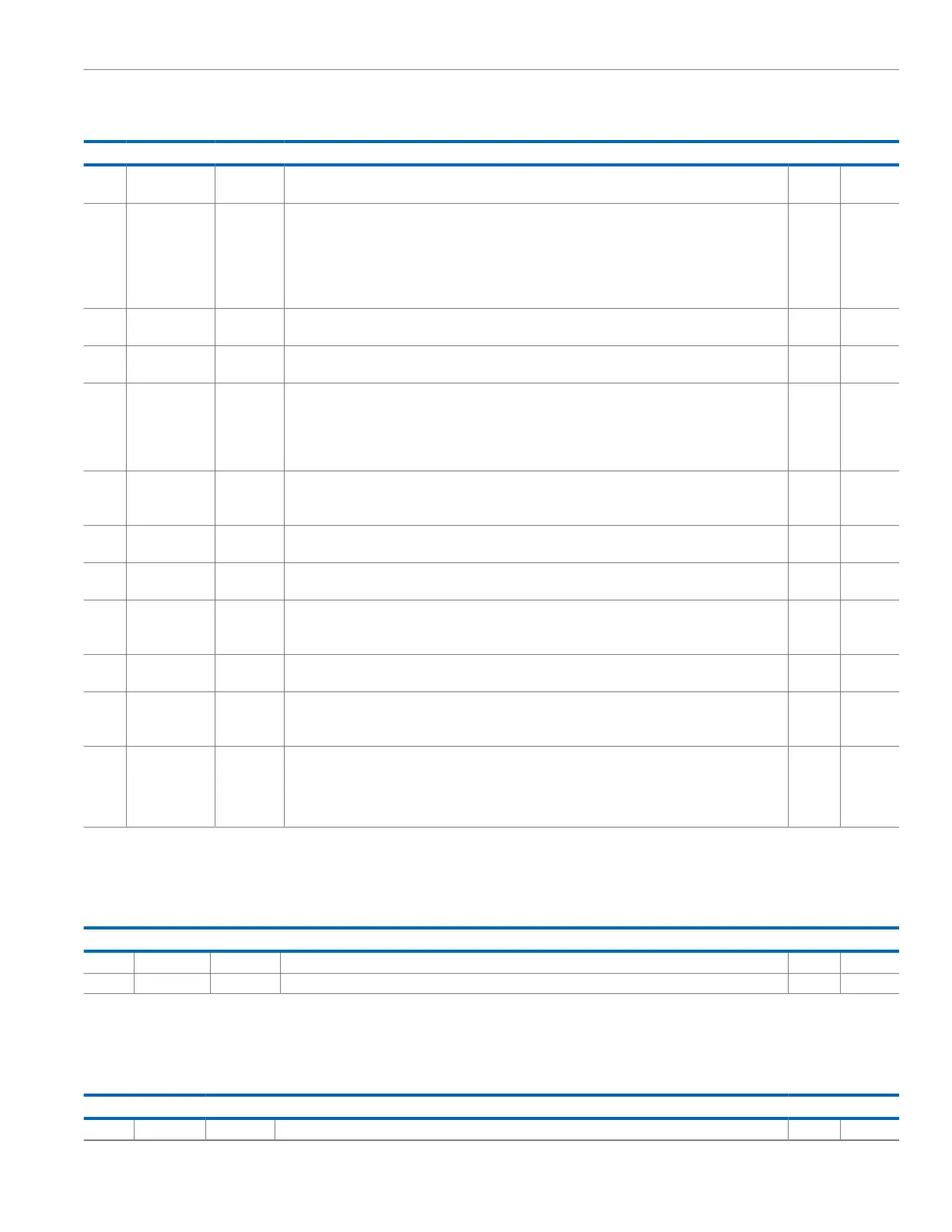

INITIATOR TRANSMIT DATA REGISTER

Address: 0x4000300C, Reset: 0x0000, Name: MTX

Table 286. Bit Descriptions for MTX

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

Loading...

Loading...