Reference Manual ADuCM356

REGISTER DETAILS: CLOCK ARCHITECTURE

analog.com Rev. A | 18 of 312

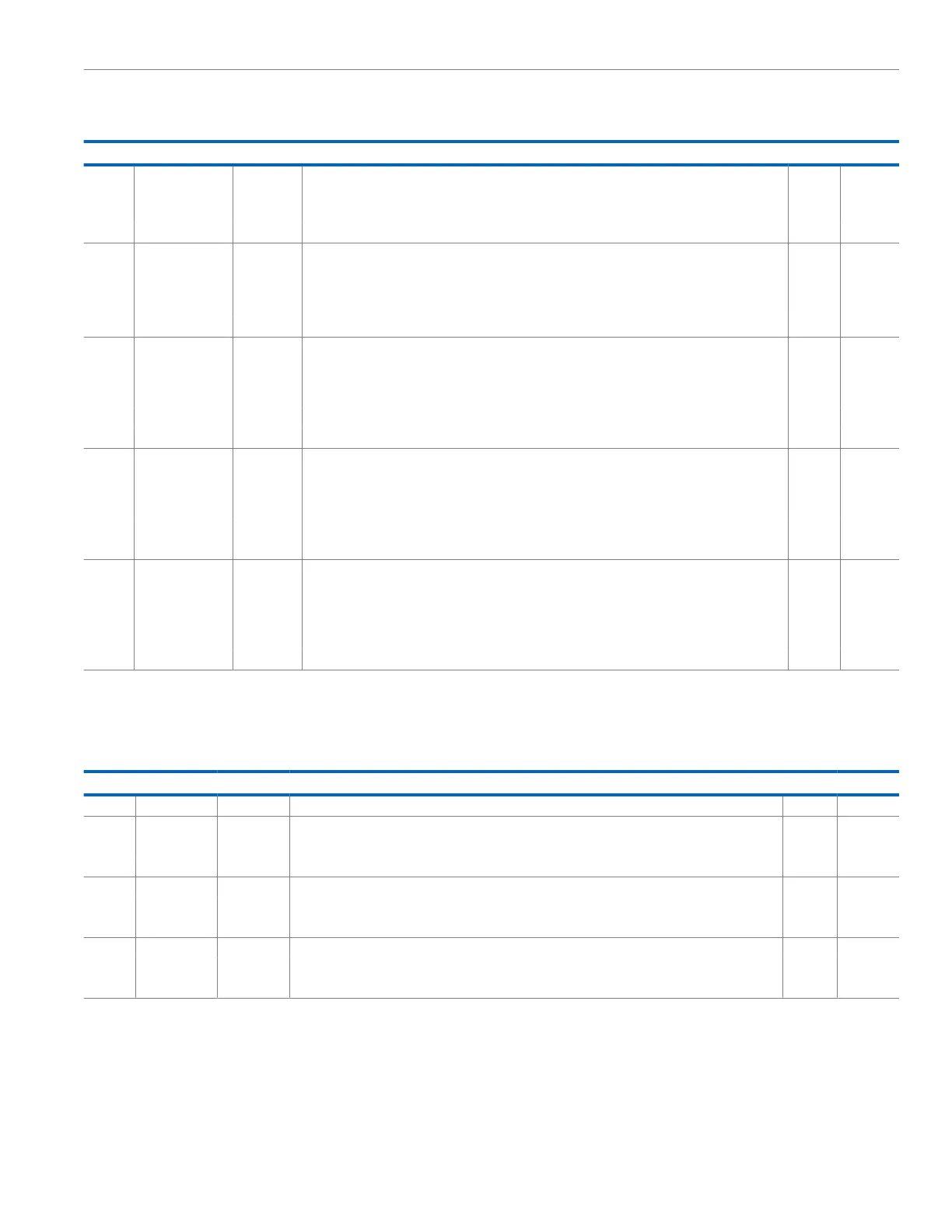

Table 9. Bit Descriptions for CTL5 (Continued)

Bits Bit Name Settings Description Reset Access

disable this bit to control ACLK out. Before programming the ACLKDIVCNT bits in the CTL1 register,

clear this bit to 0. Otherwise, the ACLKDIVCNT bit is not taken into effect.

0 GPIO clock is enabled.

1 GPIO clock is disabled.

3 UCLKI2COFF I

2

C Clock User Control. This bit disables the I

2

C universal clock (UCLK) and controls the gate on the

I

2

C UCLK in active and flexi modes. In hibernate mode, the I

2

C UCLK is always off and this bit has no

effect. This bit is automatically cleared if the user code accesses any of the I

2

C registers.

0x1 R/W

0 I

2

C clock is enabled.

1 I

2

C clock is disabled.

2 GPTCLK2OFF General-Purpose Timer 2 User Control. This bit disables the General-Purpose Timer 2 clock (muxed

version) and controls the gate in active and flexi modes. In hibernate mode, the General-Purpose

Timer 2 clock is always off and this bit has no effect. This bit is automatically cleared if user code

accesses any of the General-Purpose Timer 2 registers.

0x1 R/W

0 Timer 2 clock is enabled.

1 Timer 2 clock is disabled.

1 GPTCLK1OFF General-Purpose Timer 1 User Control. This bit disables the General-Purpose Timer 1 clock (muxed

version) and controls the gate in active and flexi modes. In hibernate mode, the General-Purpose

Timer 1 clock is always off and this bit has no effect. This bit is automatically cleared if user code

accesses any of the General-Purpose Timer 1 registers.

0x1 R/W

0 Timer 1 clock is enabled.

1 Timer 1 clock is disabled.

0 GPTCLK0OFF General-Purpose Timer 0 User Control. This bit disables the General-Purpose Timer 0 clock (muxed

version) and controls the gate in active and flexi modes. In hibernate mode, the General-Purpose

Timer 0 clock is always off and this bit has no effect. This bit is automatically cleared if user code

accesses any of the General-Purpose Timer 0 registers.

0x1 R/W

0 Timer 0 clock is enabled.

1 Timer 0 clock is disabled.

CLOCKING STATUS REGISTER

Address: 0x4004C318, Reset: 0x00000000, Name: STAT0

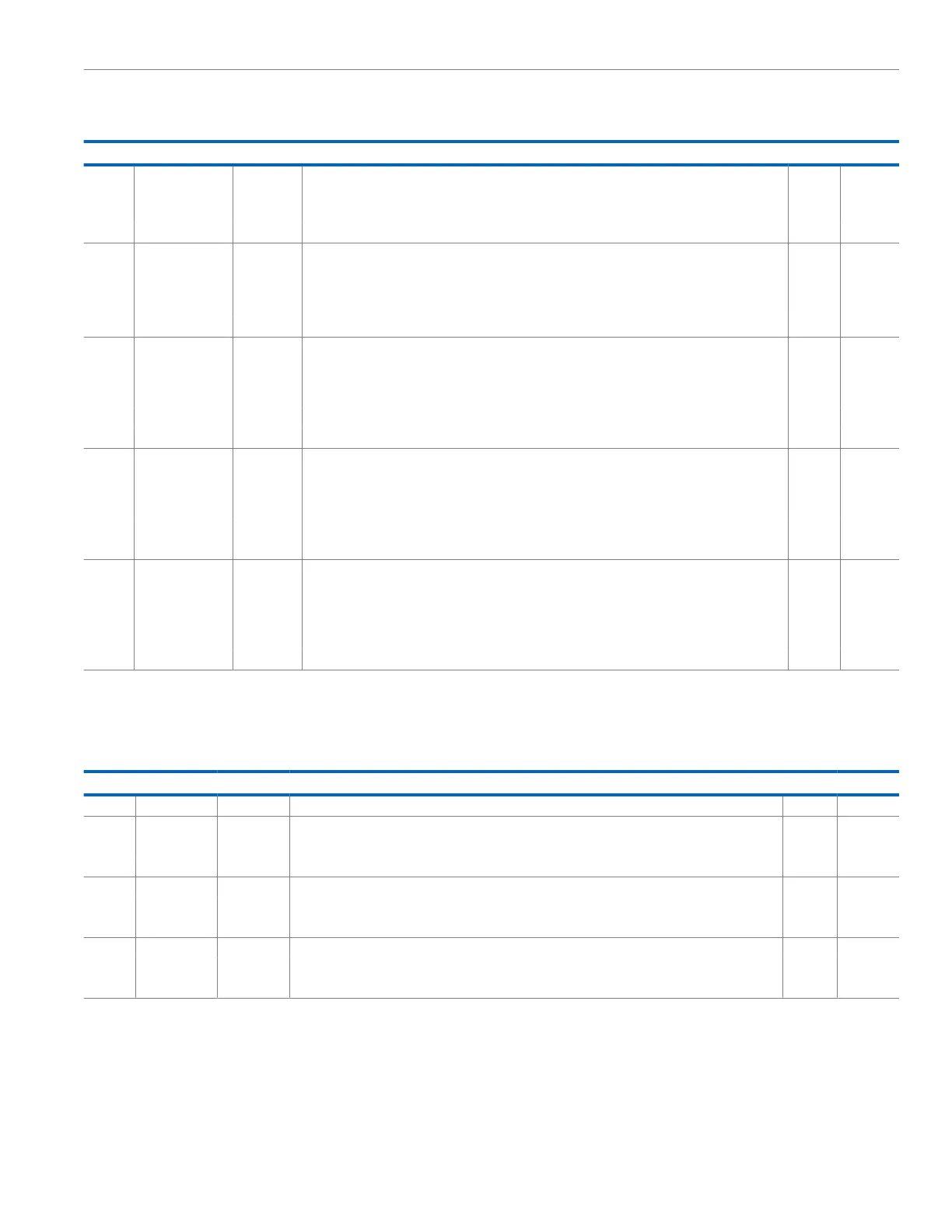

Table 10. Bit Descriptions for STAT0

Bits Bit Name Settings Description Reset Access

[15:3] Reserved Reserved. Do not write to this bit. 0 R

2 SPLLUNLK System Phase-Locked Loop (PLL) Unlock Status. Write a 1 to this bit to clear it. R/W1C

0 No loss of PLL lock detected. 0

1 A PLL loss of lock is detected.

1 SPLLLK System PLL Lock Status. Write a 1 to this bit to clear it. 0 R/W1C

0 No PLL lock event detected.

1 A PLL lock event is detected.

0 SPLL System PLL Status. 0 R

0 PLL is not locked, do not use PLL.

1 PLL is locked and ready for use.

CLOCK DIVIDER CONFIGURATION REGISTER

Address: 0x400C0408, Reset: 0x0441, Name: CLKCON0

User must write CLKCON0KEY = 0xA815 before writing to CLKCON0.

Loading...

Loading...