Reference Manual ADuCM356

REGISTER DETAILS: FLASH CACHE CONTROLLER (FLCC)

analog.com Rev. A | 195 of 312

WRITE UPPER DATA REGISTER

Address: 0x40018014, Reset: 0xFFFFFFFF, Name: KH_DATA1

This register contains the upper half of 64-bit dual-word data to be written to flash.

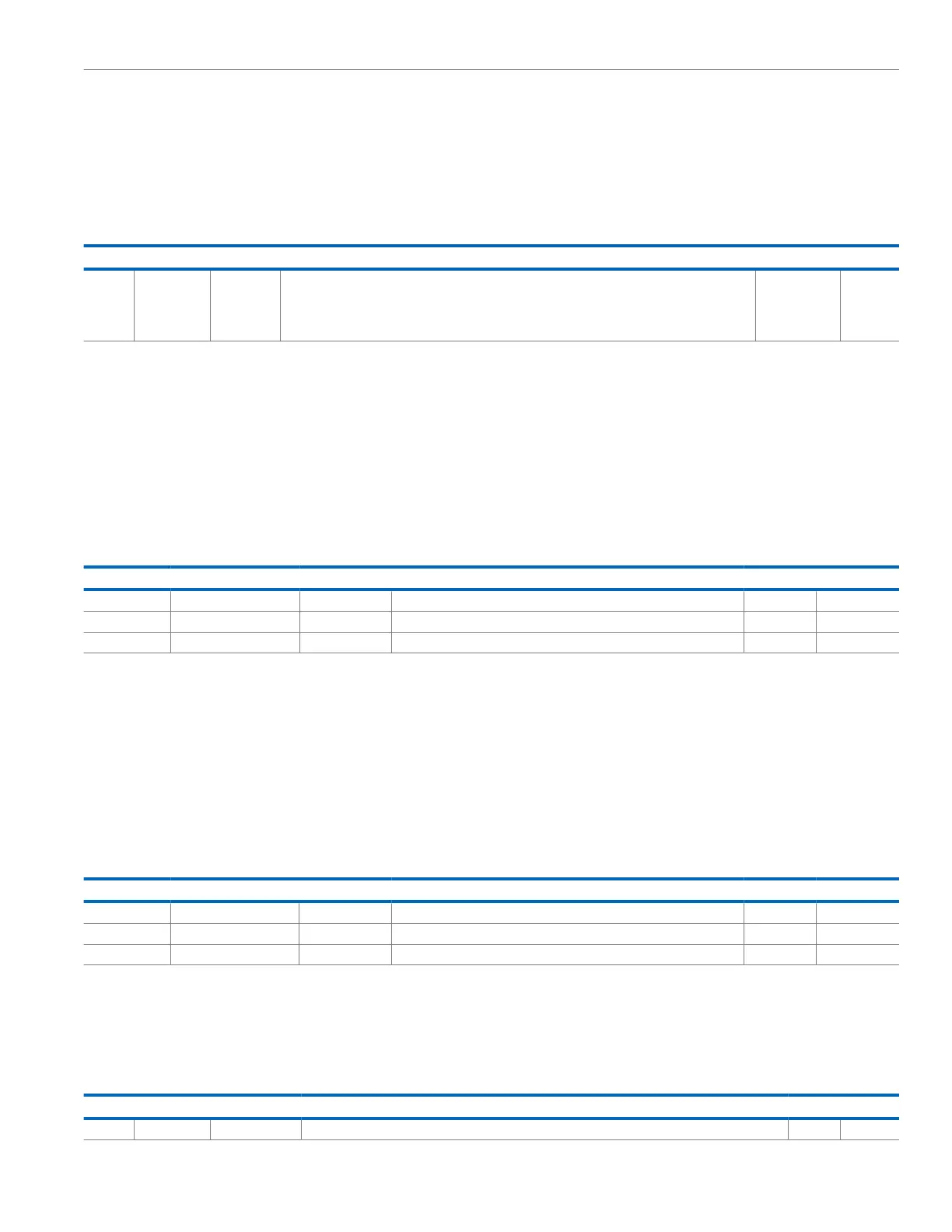

Table 229. Bit Descriptions for KH_DATA1

Bits Bit Name Settings Description Reset Access

[31:0] VALUE Upper Half of 64-Bit Dual-Word Data to Be Written on a Write Command. If DMA is enabled, this

register acts as a FIFO. Writes to this register push the old data to the lower half of 64-bit data

(KH_DATA0). When this register is written twice in DMA mode, the FIFO becomes full and a flash

write command is automatically executed.

0xFFFFFFFF R/W

LOWER PAGE ADDRESS REGISTER

Address: 0x40018018, Reset: 0x00000000, Name: PAGE_ADDR0

Write a byte address to this register to select the page in which that byte exists.

The selected page can be used for an erase page command (selecting which page to erase) or for a sign command (selecting the start page

for a block on which a signature is calculated). For commands using both the PAGE_ADDR0 register and PAGE_ADDR1 register, ensure that

PAGE_ADDR0 is always less than or equal to PAGE_ADDR1, or else the command is denied.

Writing any address above the valid range of flash memory saturates the address register to prevent aliasing in the flash memory space.

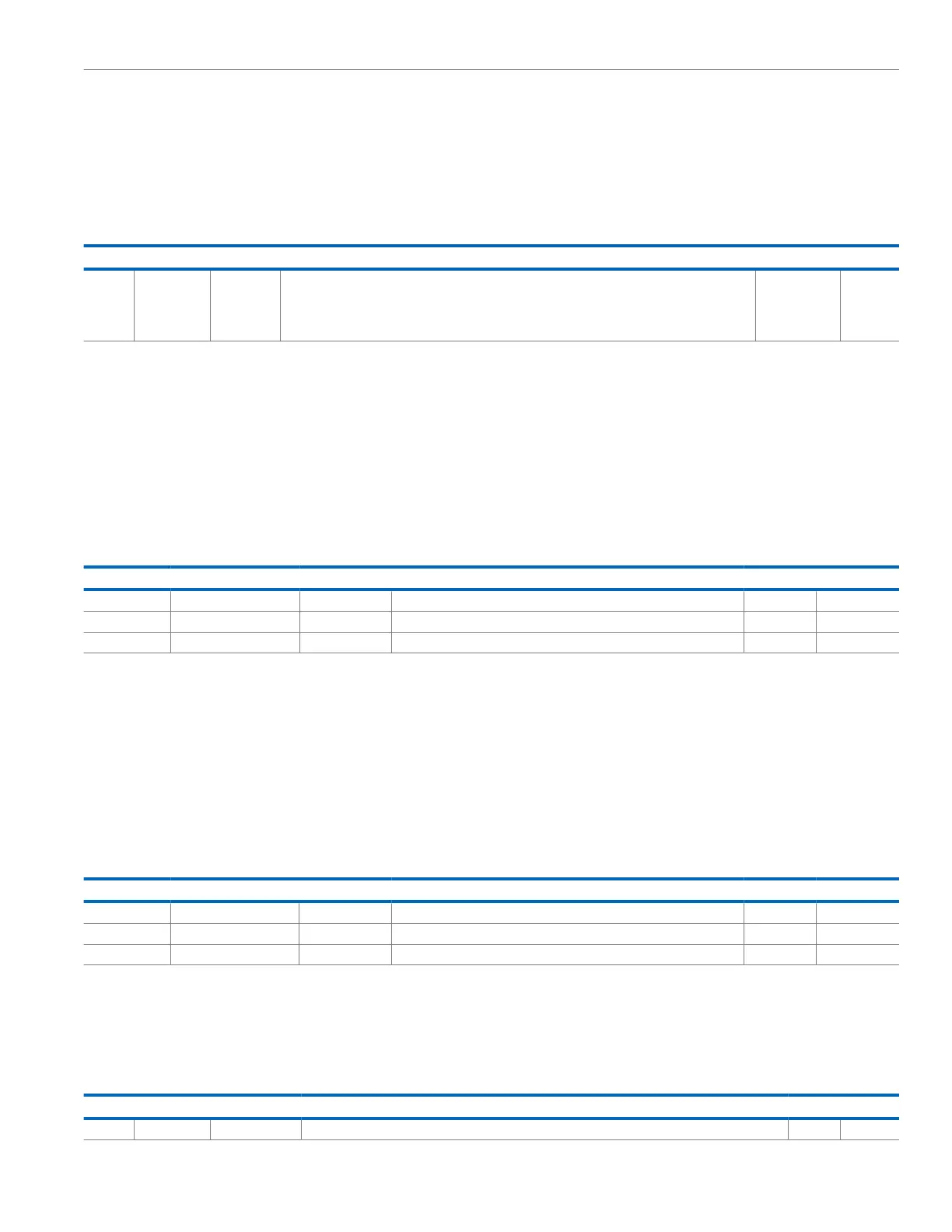

Table 230. Bit Descriptions for PAGE_ADDR0

Bits Bit Name Settings Description Reset Access

[31:19] Reserved Reserved. 0x0 R

[18:10] VALUE Lower Address Bits of the Page Address. 0x0 R/W

[9:0] Reserved Reserved. 0x0 R

UPPER PAGE ADDRESS REGISTER

Address: 0x4001801C, Reset: 0x00000000, Name: PAGE_ADDR1

Write a byte address to this register to select the page in which that byte exists.

The selected page can be used for a sign command (selecting the end page for a block on which a signature is calculated). For commands

using both the PAGE_ADDR0 register and PAGE_ADDR1 register, ensure that PAGE_ADDR0 is always less than or equal to PAGE_ADDR1,

or else the command is denied.

Writing any address above the valid range of flash memory saturates the address register to prevent aliasing in the flash memory space.

Table 231. Bit Descriptions for PAGE_ADDR1

Bits Bit Name Settings Description Reset Access

[31:19] Reserved Reserved. 0x0 R

[18:10] VALUE Upper Address Bits of the Page Address. 0x0 R/W

[9:0] Reserved Reserved. 0x0 R

KEY REGISTER

Address: 0x40018020, Reset: 0x00000000, Name: KEY

When user code writes a key to access protected features, the key value must be written to this register.

Table 232. Bit descriptions for KEY

Bits Bit Name Settings Description Reset Access

[31:0] VALUE Key Register. Unlock protected features by writing the appropriate key value to this register. 0x0 W

Loading...

Loading...