Reference Manual ADuCM356

REGISTER DETAILS: SPI0/SPI1

analog.com Rev. A | 246 of 312

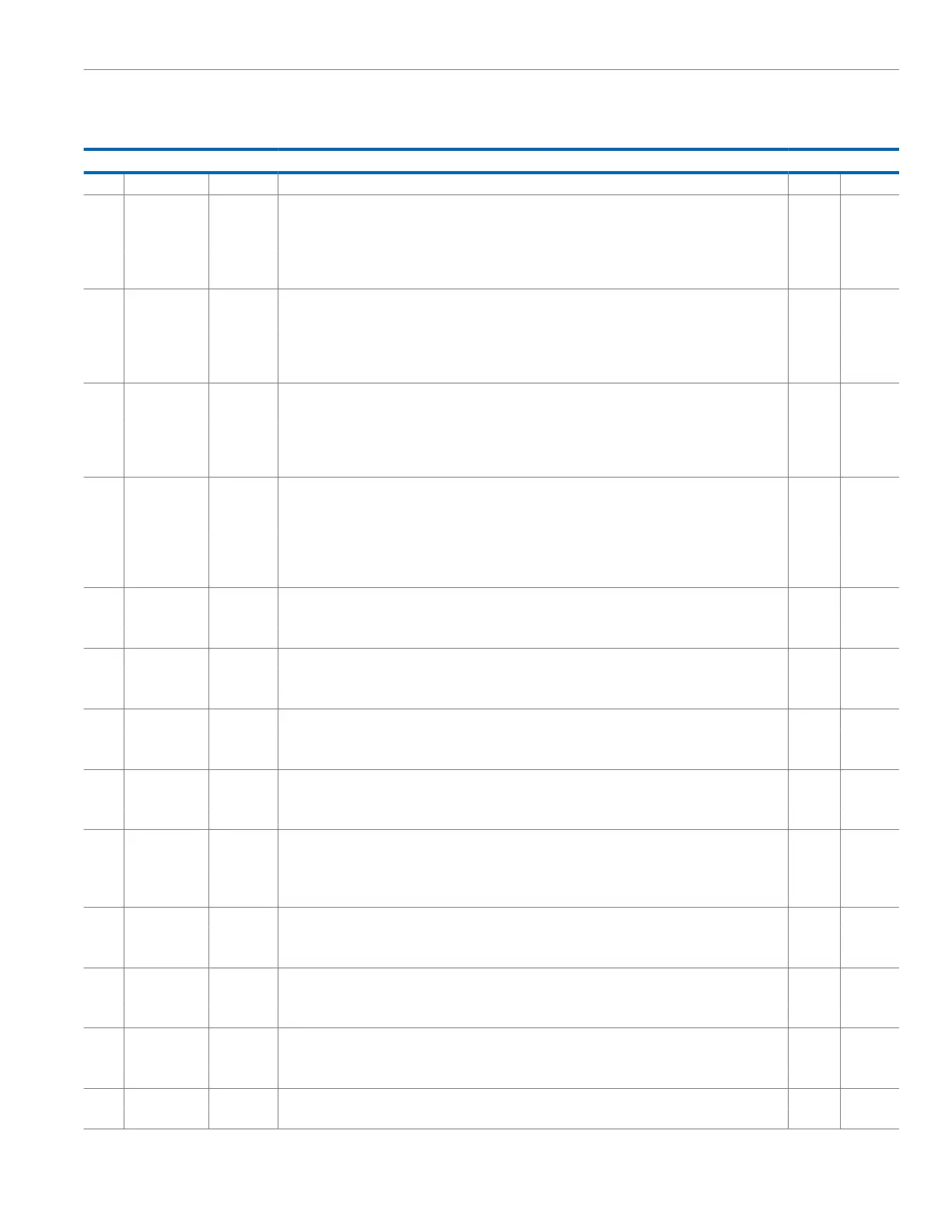

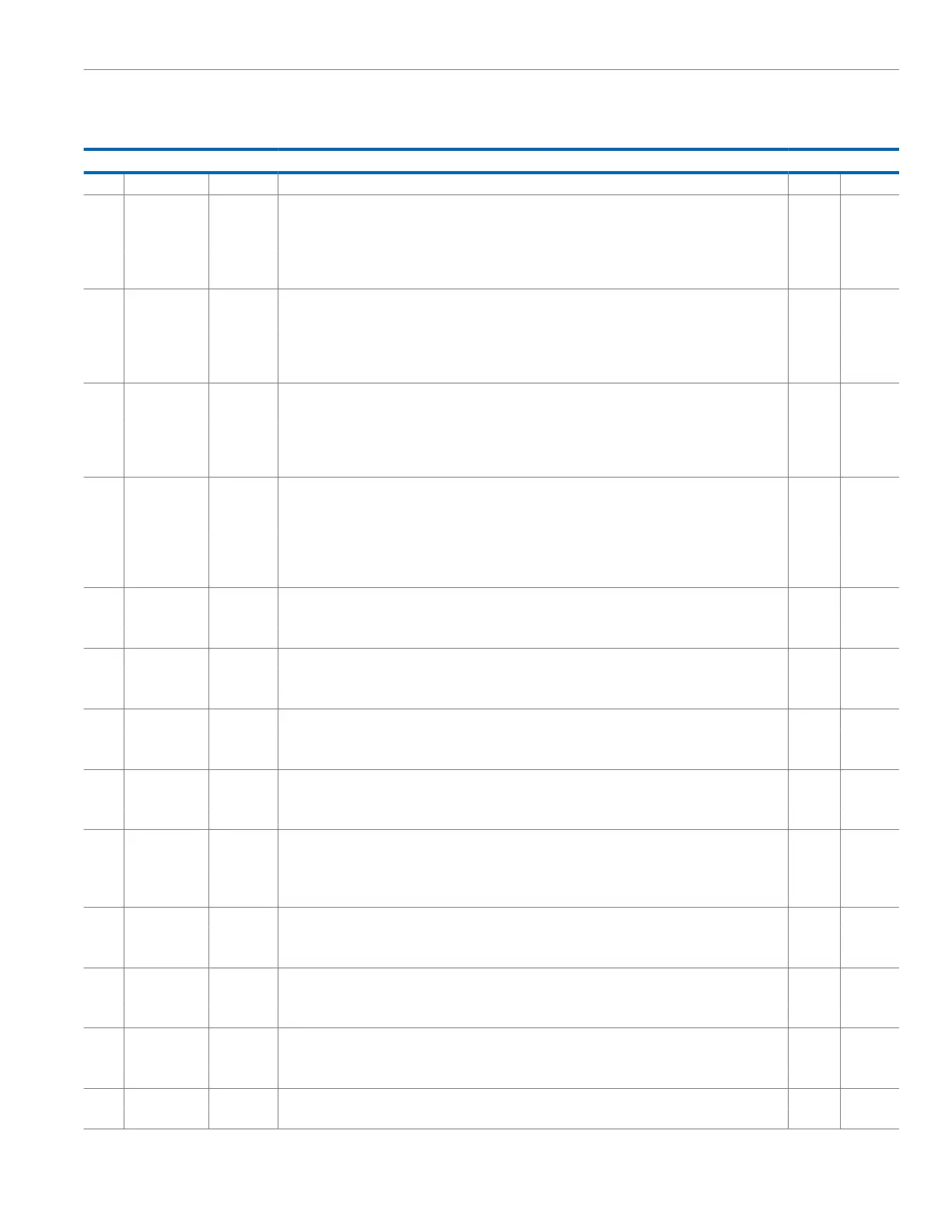

Table 310. Bit Descriptions for SPI0_CTL, SPI1_CTL

Bits Bit Name Settings Description Reset Access

15 Reserved Reserved. 0x0 R

14 CSRST Reset Mode for Chip Select Error Bit. 0x0 R/W

0 The bit counter continues from where it stopped. The SPI can receive the remaining bits when the chip

select is asserted and user code must ignore the SPIx_STAT, Bit 12 interrupt.

1 The bit counter is reset after a chip select error condition and the user code is expected to clear SPIx_CTL,

Bit 0. Set this bit for a recovery after a chip select error.

13 TFLUSH SPI Transmit FIFO Flush Enable. 0x0 R/W

0 Disable transmit FIFO flushing.

1 Flush the transmit FIFO. This bit does not clear itself and must be toggled if a single flush is required. If this

bit is left high, either the last transmitted value or 0x00 is transmitted depending on the ZEN bit. Any writes

to the transmit FIFO are ignored while this bit is set.

12 RFLUSH SPI Receive FIFO Flush Enable. 0x0 R/W

0 Disable receive FIFO flushing.

1 Flush the receive FIFO. This bit does not clear itself and must be toggled if a single flush is required. If this

bit is set, all incoming data is ignored and no interrupts are generated. If set and the TIM bit = 0, a read of

the receive FIFO initiates a transfer.

11 CON Continuous Transfer Enable. 0x0 R/W

0 Disable continuous transfer. Each transfer consists of a single 8-bit serial transfer. If valid data exists in the

SPIx_TX register, a new transfer is initiated after a stall period of one serial clock cycle.

1 Enable continuous transfer. In initiator mode, the transfer continues until no valid data is available in the

transmit FIFO. Chip select is asserted and remains asserted for the duration of each 8-bit serial transfer

until FIFO is empty.

10 LOOPBACK Loopback Enable. 0x0 R/W

0 Normal mode.

1 Connect MISO to MOSI and test software.

9 OEN Target MISO Output Enable. 0x0 R/W

0 Disable the output driver on the MISO pin. The MISO pin is open circuit when this bit is clear.

1 MISO operates as normal.

8 RXOF SPI Receive Overflow Overwrite Enable. 0x0 R/W

0 The new serial byte received is discarded.

1 The valid data in the receive register is overwritten by the new serial byte received.

7 ZEN Transmit Zeros Enable. 0x0 R/W

0 Transmit the last transmitted value when there is no valid data in the transmit FIFO.

1 Transmit 0x00 when there is no valid data in the transmit FIFO.

6 TIM SPI Transfer and Interrupt Mode. 0x0 R/W

0 Initiate transfer with a read of the SPIx_RX register. An interrupt only occurs when the receive FIFO is full.

1 Initiate transfer with a write to the SPIx_TX register. An interrupt only occurs when the transmit FIFO is

empty.

5 LSB LSB First Transfer Enable. 0x0 R/W

0 MSB transmitted first.

1 LSB transmitted first.

4 WOM SPI Wire-OR’ed Mode. 0x0 R/W

0 Normal output levels.

1 Enables open circuit data output enable. External pull-up resistors required on data out pins.

3 CPOL Serial Clock Polarity. 0x0 R/W

0 Serial clock idles low.

1 Serial clock idles high.

2 CPHA Serial Clock Phase Mode. 0x0 R/W

0 Serial clock pulses at the end of each serial bit transfer.

Loading...

Loading...