Reference Manual ADuCM356

REGISTER DETAILS: DIGITAL DIE WAKE-UP TIMER

analog.com Rev. A | 297 of 312

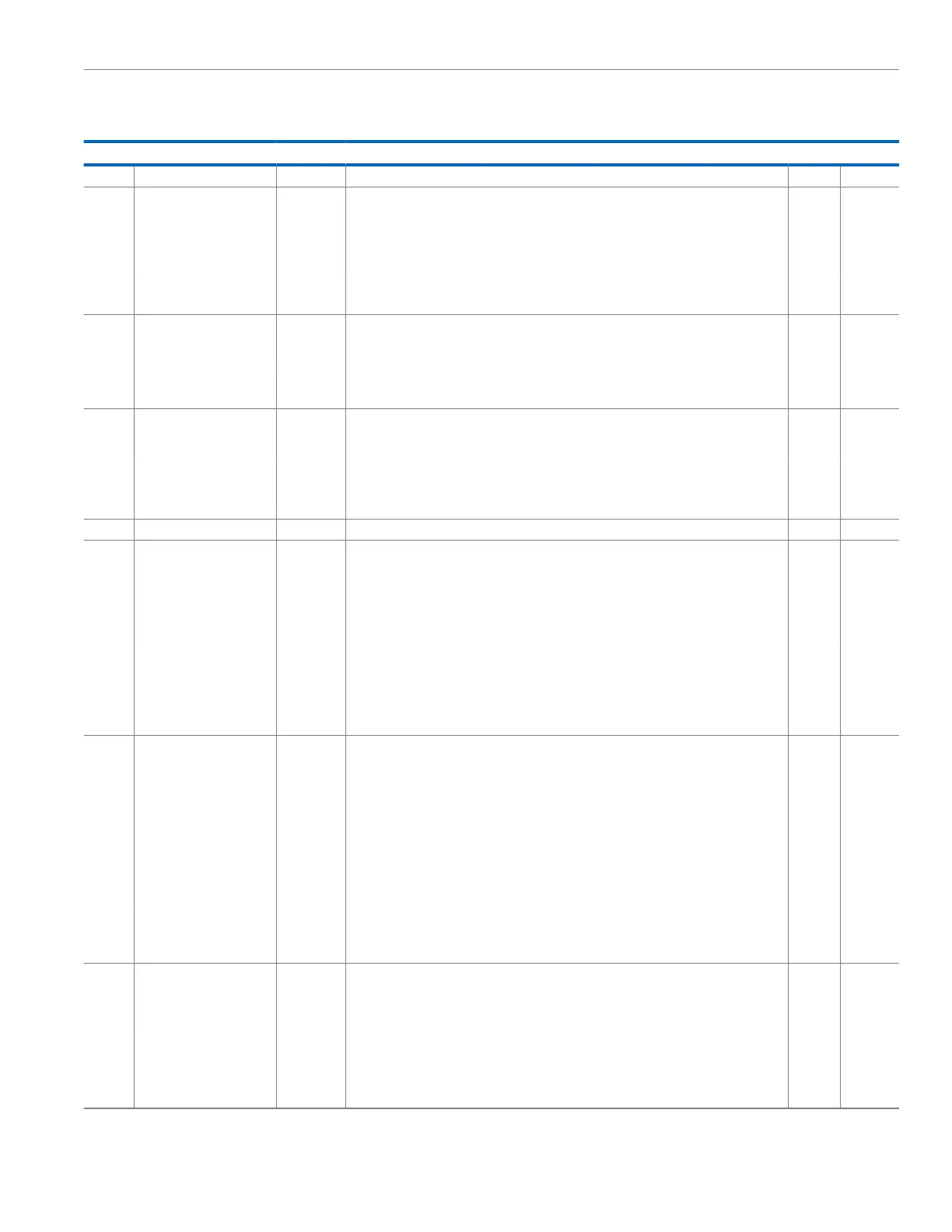

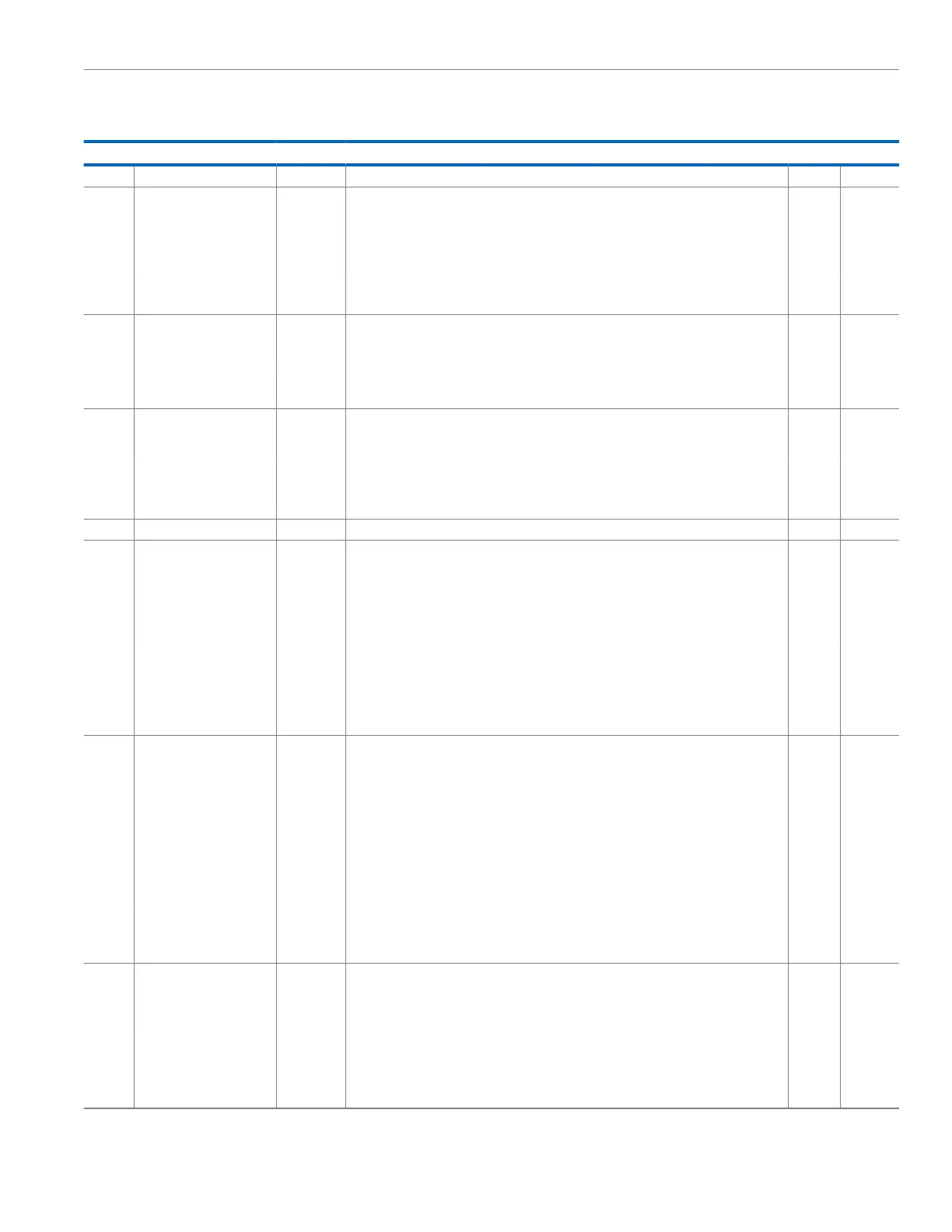

Table 389. Bit Descriptions for SR2 (Continued)

Bits Bit Name Settings Description Reset Access

1 Results of a posted write to CR1 are visible to the CPU.

14 WSYNCCR1MIR Synchronization Status of Posted Writes to CR1. This bit indicates if the effects of a posted

write to CR1 are visible to the CPU. If this bit is low, a posted write to CR1 is currently

queued up or in the process of being executed, but the results of this transaction are not

yet visible to the CPU. When this bit goes high and thereby activates the SR0, Bit 5 sticky

interrupt source, the effects of a write to CR1 are then available to the processor.

0x1 R

0 Results of a posted write to CR1 are not yet visible to the CPU.

1 Results of a posted write to CR1 are visible to the CPU.

13 WPNDALM2MIR Pending Status of Posted Writes to ALM2. This bit indicates if a posted register write to

ALM2 is currently pending and awaiting execution, meaning that no further write to the same

MMR can be accepted at this time.

0x0 R

0 Results of a posted write to CR1 are not yet visible by the CPU.

1 Results of a posted write to CR1 are visible by the CPU.

12 WPNDCR1MIR Pending Status of Posted Writes to CR1. This bit indicates if a posted register write to CR1

is currently pending and awaiting execution, meaning that no further write to the same MMR

can be accepted at this time.

0x0 R

0 The WUT can accept a new posted write to CR1.

1 A previously posted write to CR1 is still awaiting execution. No new posting to this MMR can

be accepted.

[11:7] Reserved Reserved. 0x0 R

6 CNTMOD60ROLL WUT Count Modulo 60 Roll Over. When the CPU reacts to an interrupt due to the CR1, Bit

4 interrupt source, or if the CPU sees CR1, Bit 4 stickily set, the CPU can use this bit to

confirm if the value of CNTMOD60 in the MOD register is still reflective of the roll over or

has moved on since the actual occurrence. The latter is the case if the CPU was tardy in

its response to a WUT interrupt caused by CR1, Bit 4 or if CR1, Bit 4 was not enabled as a

contributory interrupt source for the RTC.

0x0 R

0 The modulo 60 value of the WUT real-time count in CNTMOD60 has not risen due to a roll

over.

1 The modulo 60 value of the WUT real-time count currently in CNTMOD60 has rolled over

from a value at or within trimming distance of its maximum to a value at or within trimming

distance of its minimum.

5 CNTROLL WUT Count Roll Over. CNTROLL indicates whether the current value of the WUT real-time

count given by CNT1, CNT0, and CNT2 is due to a rollover from its maximum possible value

to its minimum possible value when incremented at the most recent prescaled time unit.

When the CPU reacts to an interrupt due to the CNTROLLINT interrupt source or sees that

CNTROLLINT is stickily set, the CPU can use this bit to confirm if the values in CNT1, CNT0,

and CNT2 are still reflective of the roll over or have moved on since the actual occurrence.

The latter is the case if the CPU was tardy in its response to a WUT interrupt caused by

CNTROLLINT or if CNTROLLINT was not enabled as a contributory interrupt source for the

RTC.

0x0 R

0 The WUT real-time count in CNT1, CNT0, and CNT2 has not risen due to a roll over.

1 The WUT real-time count currently in CNT1, CNT0, and CNT2 has rolled over from a value

at or within trimming distance of its maximum to a value at or within trimming distance of its

minimum.

4 CNTMOD60ROLLINT WUT Modulo 60 Count Roll Over Interrupt Source. This bit sticks active high when the

modulo 60 equivalent of the CNT1 and CNT0 count value rolls over from 59 to zero. Such a

roll over event happens every 60 prescaled increments of the WUT count, or fewer if positive

trimming is active.

0x0 R/W1C

0 The modulo 60 value of CNT1 and CNT0 in CNTMOD60 has not rolled over since this bit

was last cleared.

1 The modulo 60 value of CNT1 and CNT0 in CNTMOD60 has rolled over since this bit was

last cleared.

Loading...

Loading...