Reference Manual ADuCM356

AFE INTERRUPTS

analog.com Rev. A | 138 of 312

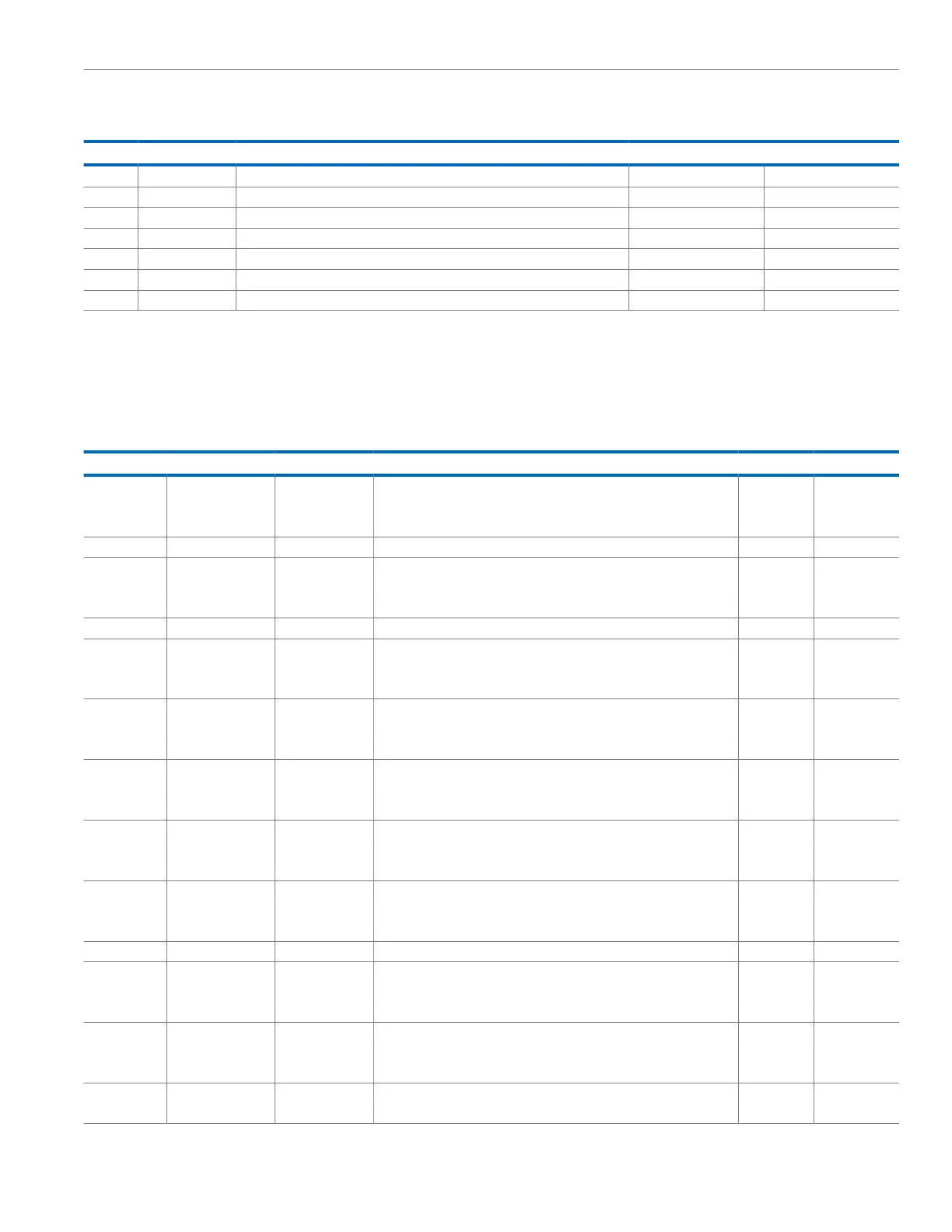

Table 176. Bit Descriptions for INTCCLR Register (Continued)

Bits Bit Name Description Reset Access

6 INTCLR6 ADC Delta Fail IRQ. Write 1 to clear. 0x0 W

5 INTCLR5 ADC Maximum Fail IRQ. Write 1 to clear. 0x0 W

4 INTCLR4 ADC Minimum Fail IRQ. Write 1 to clear. 0x0 W

3 INTCLR3 Temperature Result IRQ. Write 1 to clear. 0x0 W

2 INTCLR2 Sinc2 Filter Result Ready IRQ. Write 1 to clear. 0x0 W

1 INTCLR1 DFT Result IRQ. Write 1 to clear. 0x0 W

0 INTCLR0 ADC Result IRQ. Write 1 to clear. 0x0 W

Interrupt Controller Select Registers

Address: 0x400C3008, Reset: 0x00002000, Name: INTCSEL0

Address: 0x400C300C, Reset: 0x00002000, Name: INTCSEL1

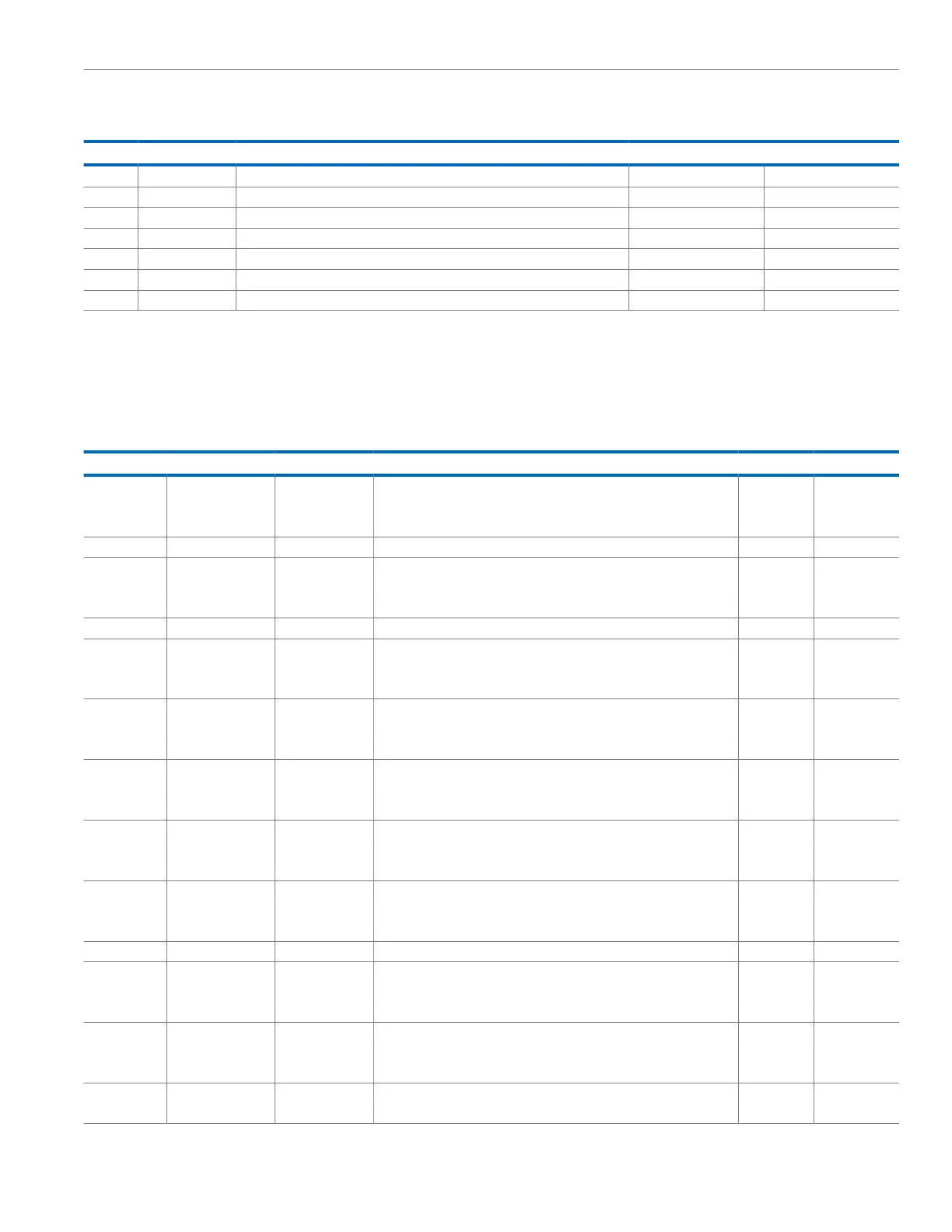

Table 177. Bit Descriptions for INTCSEL0 and INTCSEL1 Registers

Bits Bit Name Settings Description Reset Access

31 INTSEL31 Attempt to Break IRQ Enable. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

30 Reserved Reserved. 0x0 R/W

29 INTSEL29 Outlier IRQ Enable. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

28 Reserved Reserved. 0x0 R/W

27 INTSEL27 Data FIFO Underflow IRQ Enable. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

26 INTSEL26 Data FIFO Overflow IRQ Enable. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

25 INTSEL25 Data FIFO Threshold IRQ Enable. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

24 INTSEL24 Data FIFO Empty IRQ Enable. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

23 INTSEL23 Data FIFO Full IRQ Enable. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

[22:18] Reserved Reserved. 0x0 R/W

17 INTSEL17 Sequencer Timeout Error IRQ Enable. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

16 INTSEL16 Sequencer Timeout Finished IRQ Enable. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

15 INTSEL15 End of Sequence IRQ Enable. 0x0 R/W

0 Interrupt disabled.

Loading...

Loading...