Reference Manual ADuCM356

SLEEP AND WAKE-UP TIMER

analog.com Rev. A | 147 of 312

Address: 0x400C0820, Reset: 0xFFFF, Name: SEQ1SLEEPL

Address: 0x400C0830, Reset: 0xFFFF, Name: SEQ2SLEEPL

Address: 0x400C0840, Reset: 0xFFFF, Name: SEQ3SLEEPL

The SEQxSLEEPL registers define the device active time for SEQ0 to SEQ3. The counter is 20 bits. These registers set the 16 LSBs.

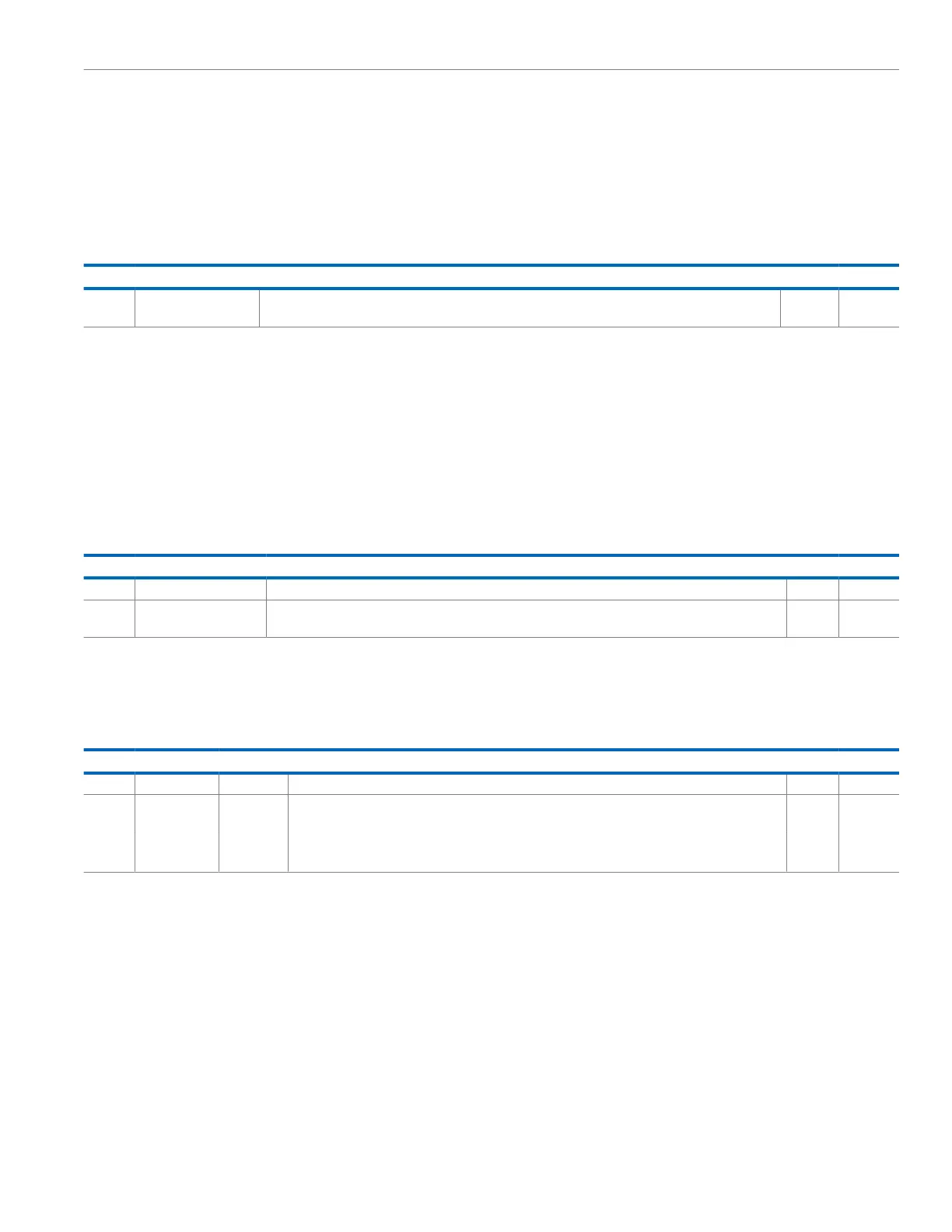

Table 185. Bit Descriptions for SEQxSLEEPL Registers

Bits Bit Name Description Reset Access

[15:0] SLEEPTIME0[15:0] Sequence and Active Period. This register defines the length of time in which the device stays in active mode.

When this time elapses, the device returns to a sleep state.

0xFFFF R/W

Sequence 0 to Sequence 3 Sleep Time Registers (MSB)

Address: 0x400C0814, Reset: 0x000F, Name: SEQ0SLEEPH

Address: 0x400C0824, Reset: 0x000F, Name: SEQ1SLEEPH

Address: 0x400C0834, Reset: 0x000F, Name: SEQ2SLEEPH

Address: 0x400C0844, Reset: 0x000F, Name: SEQ3SLEEPH

The SEQxSLEEPH registers define the device active time for SEQ0 to SEQ3. The counter is 20 bits. These registers set the four MSBs.

Table 186. Bit Descriptions for SEQxSLEEPH Registers

Bits Bit Name Description Reset Access

[15:4] Reserved Reserved. 0x0 R

[3:0] SLEEPTIME0[19:16] Sequence and Active Period. These bits define the length of time in which the device stays in active mode.

When this time elapses, the device returns to a sleep state.

0xF R/W

Timer Wake-Up Configuration Register

Address: 0x400C0A1C, Reset: 0x0000, Name: TMRCON

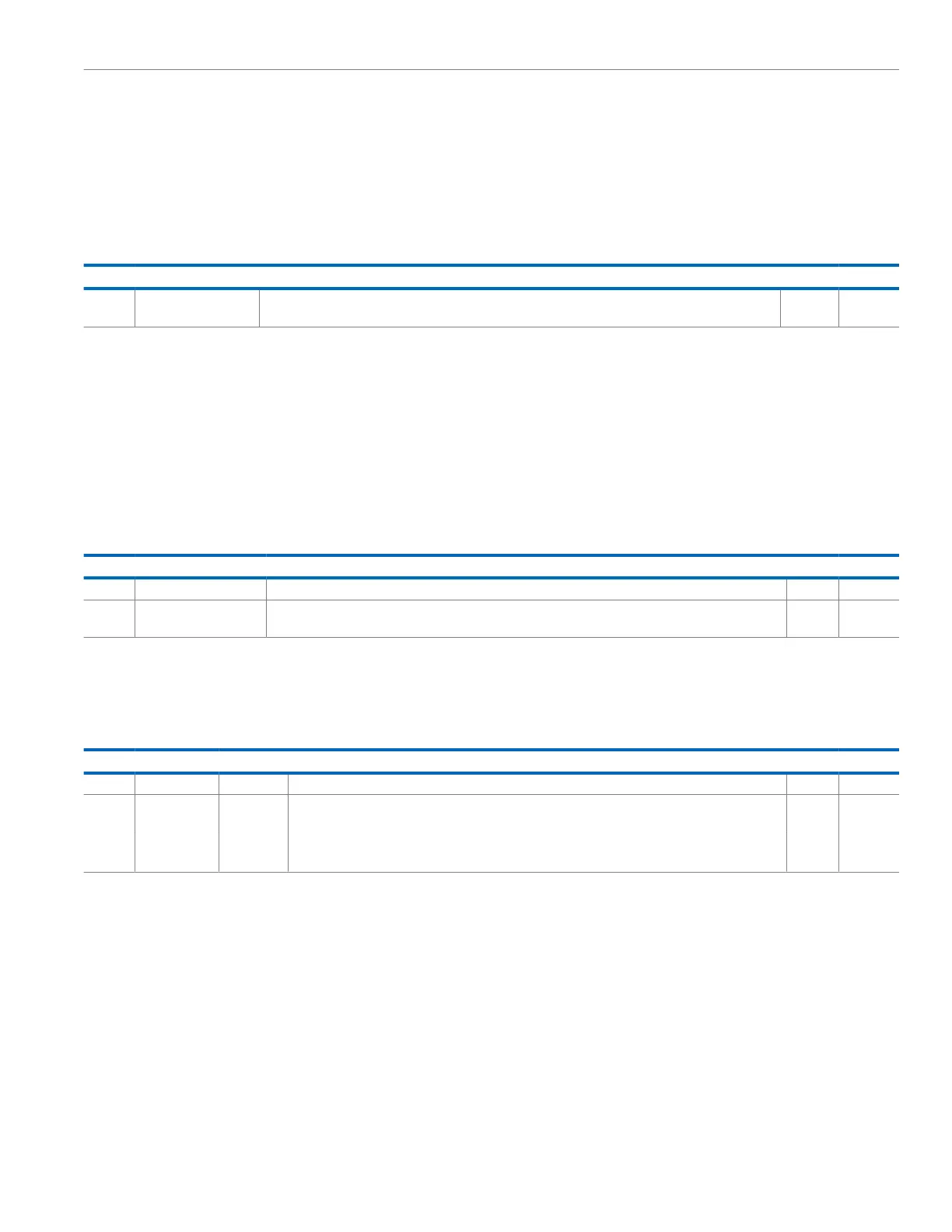

Table 187. Bit Descriptions for TMRCON Register

Bits Bit Name Settings Description Reset Access

[15:1] Reserved Reserved. 0x0 R

0 TMRINTEN Wake-Up Timer Enable. Set this bit before entering hibernate mode to enable the ability of the sleep and

wake-up timer to wake up the chip.

0x0 R/W

0 Wake-up timer disabled.

1 Wake-up timer enabled.

Loading...

Loading...