Reference Manual ADuCM356

REGISTER DETAILS: DIGITAL DIE WAKE-UP TIMER

analog.com Rev. A | 292 of 312

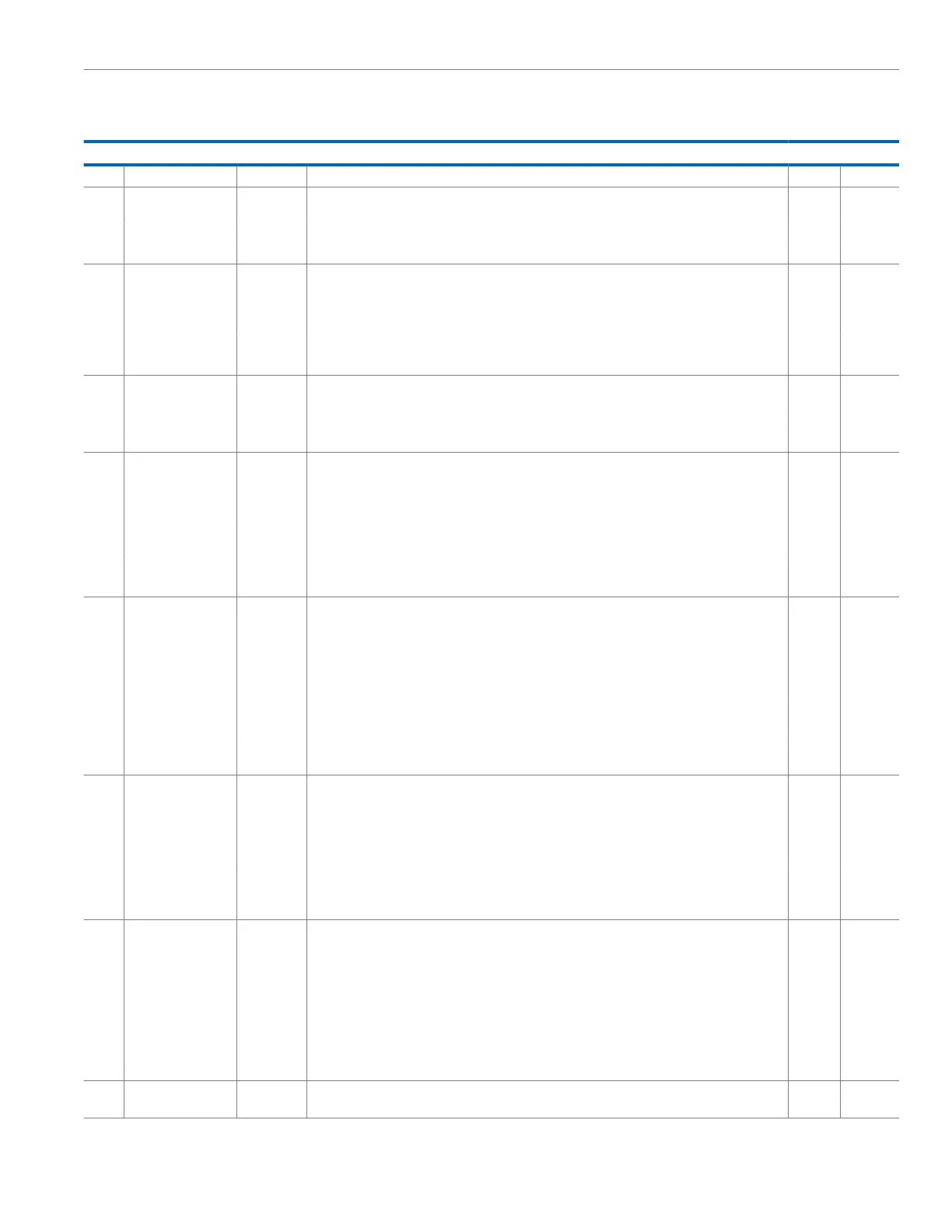

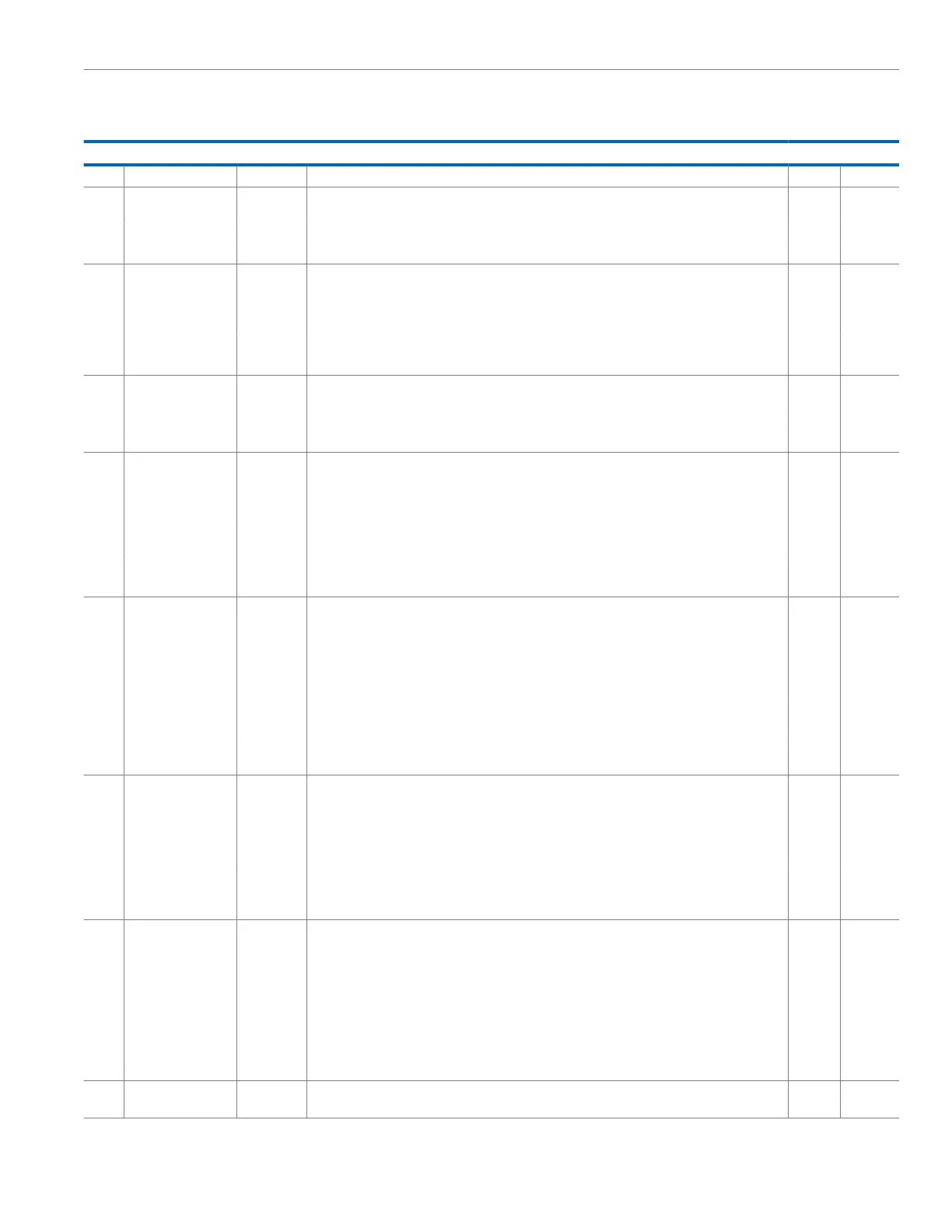

Table 381. Bit Descriptions for SR0 (Continued)

Bits Bit Name Settings Description Reset Access

1 Results of a posted write are visible to the CPU.

9 WSYNCCNT0 Synchronization Status of Posted Writes to the CNT0 Register. WSYNCCNT0 indicates if the effects

of a posted write to CNT0 are visible to the CPU.

0x1 R

0 Results of a posted write are not yet visible to the CPU.

1 Results of a posted write are visible to the CPU.

8 WSYNCSR0 Synchronization Status of Posted Clearances to Interrupt Sources in the SR0 Register. WSYNCSR0

indicates if the effects of a posted write to SR0 are visible to the CPU. No posting or associated

masking is needed for clearances of the WPNDERRINT, WSYNCINT, and WPENDINT bits in SR0,

because these fields are sourced in the clock domain of the core. Their clearance is immediate.

0x1 R

0 Results of a posted write are not yet visible to the CPU.

1 Results of a posted write are visible to the CPU.

7 WSYNCCR0 Synchronization Status of Posted Writes to the CR0 Register. WSYNCCR0 indicates if the effects of a

posted write to CR0 are visible to the CPU.

0x1 R

0 Results of a posted write are not yet visible by the CPU.

1 Results of a posted write are visible by the CPU.

6 WPENDINT Write Pending Interrupt. WPENDINT is a sticky interrupt source that is activated whenever there is

room in the CPU to post a new write transaction to a 32 kHz sourced MMR or MMR bit field in

the RTC. To enable a WPENDINT interrupt, set WPENDINTEN to 1 in the CR0 register. Cleared by

writing a value of one to this bit.

0x0 R/W1C

0 There has been no change in the pending status of any posted write transaction in the WUT since

WPENDINT was last cleared.

1 A posted write transaction has been dispatched since WPENDINT was last cleared, freeing up a slot

for a new posted write by the CPU to the same MMR.

5 WSYNCINT Write Synchronization Interrupt. WSYNCINT is a sticky interrupt source that is activated whenever a

posted write transaction to a 32 kHz sourced MMR or MMR bit field completes and whose effects

are then visible to the CPU. By checking the synchronization status of posted write bits of SR0

(Bits[12:7]) and SR2 (Bits[15:14]), the CPU can identify which posted write transaction has just

completed and caused the WSYNCINT interrupt source to stick (or restick if already active). Cleared

by writing 1 to this bit.

0x0 R/W1C

0 Since the CPU last cleared WSYNCINT, there has been no occurrence of the effects of a posted write

transaction to a 32 kHz sourced MMR or MMR bit field.

1 Since the CPU last cleared WSYNCINT, the effects of a posted write transaction to a 32 kHz sourced

MMR or MMR bit field has become newly visible to the clock domain of the CPU.

4 WPNDERRINT Write Pending Error Interrupt Source. This bit is a sticky interrupt source that indicates that an error

has occurred because the CPU attempted to write to a WUT register while a previous write to the

same register was pending execution. If multiple write pending errors occur, WPNDERRINT sticks at

the first occurrence. Cleared by writing 1 to this bit.

0x0 R/W1C

0 No posted write has been rejected by the WUT since WPNDERRINT was last cleared by the CPU.

1 A posted write has been rejected by the WUT due to a previously posted write to the same

MMR, which is still awaiting execution. Such a rejection has occurred since the CPU last cleared

WPNDERRINT.

3 ISOINT WUT Power Domain Isolation Interrupt Source. ISOINT is a sticky interrupt source that indicates

whether the WUT has had to activate its power domain isolation barrier due to a power loss in the

core. When the core regains power, the CPU can read ISOINT to inform itself of such a power event.

Cleared by writing a value of one to this bit.

0x1 R/W1C

0 The always on WUT power domain has not activated its isolation from the core since the ISOINT

interrupt source was last cleared by the CPU.

1 The always on WUT power domain has activated and subsequently deactivated its isolation from the

core due to a power event. This event occurred since ISOINT was last cleared by the CPU. Clear bit

by writing a 1.

2 MOD60ALMINT Modulo 60 WUT Alarm Interrupt Source. MOD60ALMINT is a sticky flag that is the source of an

optionally enabled interrupt to the CPU. This interrupt is activated once every 60 increments of CNT1

0x0 R/W1C

Loading...

Loading...