Reference Manual ADuCM356

SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS

analog.com Rev. A | 40 of 312

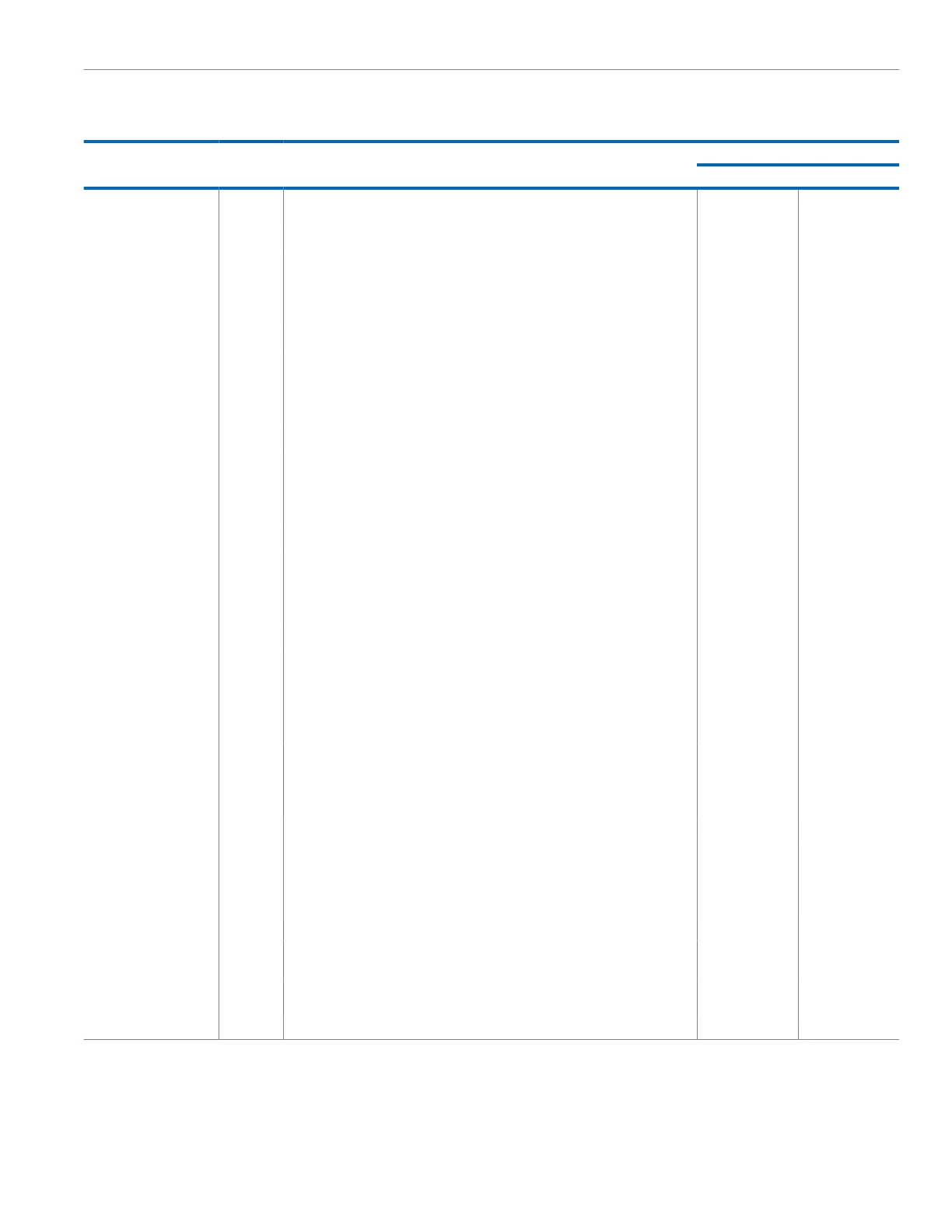

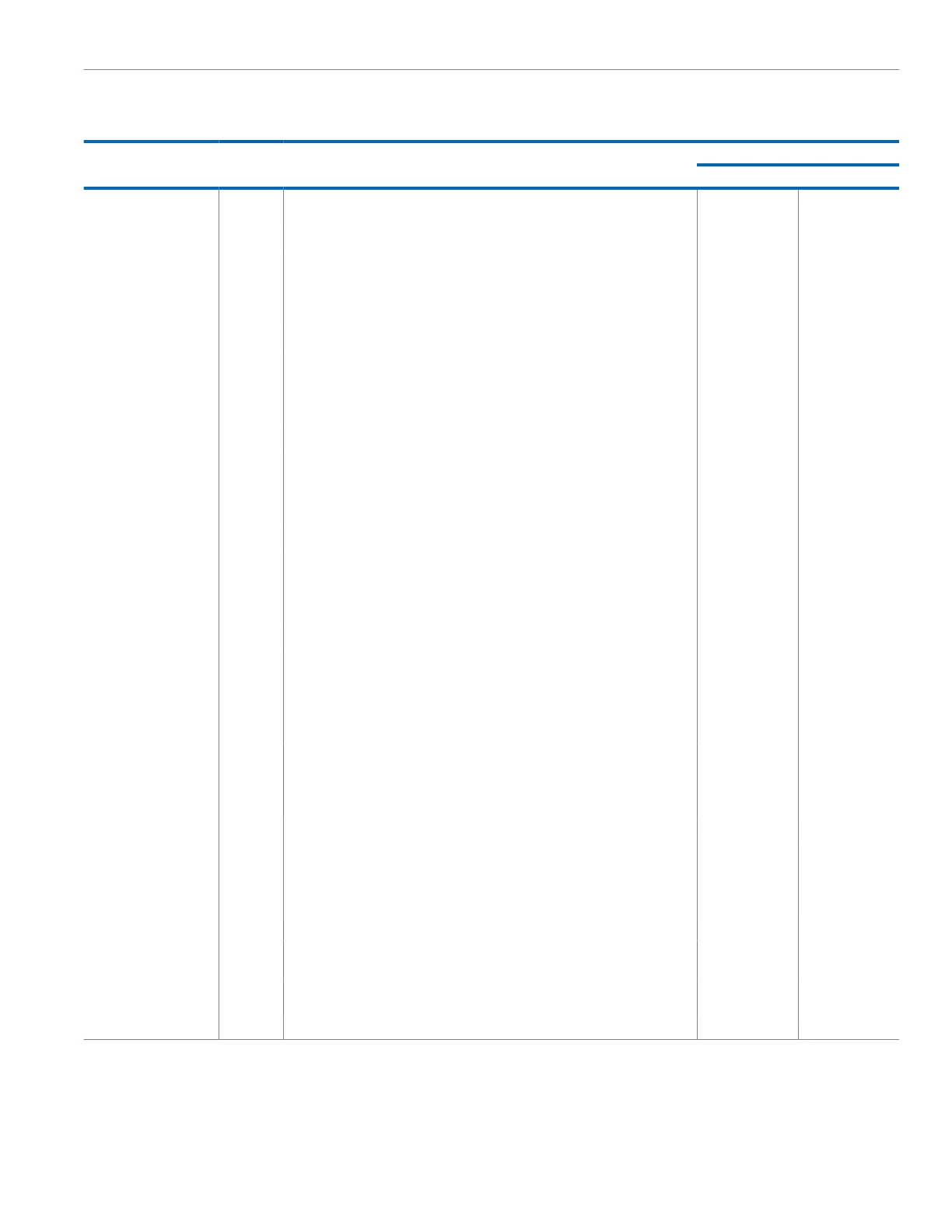

Table 41. Interrupt Vectors (Continued)

Exception Number IRQx Vector

Wake Up From

Flexi Hibernate

35 IRQ19 DMA Error Yes No

36 IRQ20 DMA Channel 0 done Yes No

37 IRQ21 DMA Channel 1 done Yes No

38 IRQ22 DMA Channel 2 done Yes No

39 IRQ23 DMA Channel 3 done Yes No

40 IRQ24 DMA Channel 4 done Yes No

41 IRQ25 DMA Channel 5 done Yes No

42 IRQ26 DMA Channel 6 done Yes No

43 IRQ27 DMA Channel 7 done Yes No

44 IRQ28 DMA Channel 8 done Yes No

45 IRQ29 DMA Channel 9 done Yes No

46 IRQ30 DMA Channel 10 done Yes No

47 IRQ31 DMA Channel 11 done Yes No

48 IRQ32 DMA Channel 12 done Yes No

49 IRQ33 DMA Channel 13 done Yes No

50 IRQ34 DMA Channel 14 done Yes No

51 IRQ35 DMA Channel 15 done Yes No

52 IRQ36 Reserved Not applicable Not applicable

53 IRQ37 Reserved Not applicable Not applicable

54 IRQ38 Reserved Yes No

55 IRQ39 Reserved Not applicable Not applicable

56 IRQ40 Digital Die General-Purpose Timer 2 Yes No

57 IRQ41 Digital die crystal oscillator Yes No

58 IRQ42 Reserved Not applicable Not applicable

59 IRQ43 Reserved Not applicable Not applicable

60 IRQ44 Reserved Yes No

61 to 63 IRQ45 to

IRQ47

Reserved Not applicable Not applicable

64 IRQ48 Analog die ADC Yes No

65 to 67 IRQ49 to

IRQ51

Reserved Not applicable Not applicable

68 IRQ52 Analog die watchdog timer Yes No

69 IRQ53 Reserved Not applicable Not applicable

70 IRQ54 Analog Die General-Purpose Timer 0 Yes No

71 IRQ55 Analog Die General-Purpose Timer 1 Yes No

72 IRQ56 Reserved Not applicable Not applicable

73 IRQ57 DMA analog die data FIFO (DMA Channel 17) Yes No

74 IRQ58 DMA Channel 18 done Yes No

75 IRQ59 DMA Channel 19 done Yes No

76 IRQ60 DMA Channel 20 done Yes No

77 IRQ61 DMA Channel 21 done Yes No

78 IRQ62 DMA Channel 22 done Yes No

79 IRQ63 DMA Channel 23 done Yes No

1

The corresponding PCLK is required to generate the interrupt.

Internal to the Arm Cortex-M3 processor, the highest user-program-

mable priority (0) is treated as fourth priority after a reset, an NMI,

or a hard fault. The ADuCM356 implements three priority bits,

which means that eight priority levels are available as programma-

ble priorities. The default for all the programmable priorities is 0.

If the same priority level is assigned to two or more interrupts,

Loading...

Loading...