Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 181

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

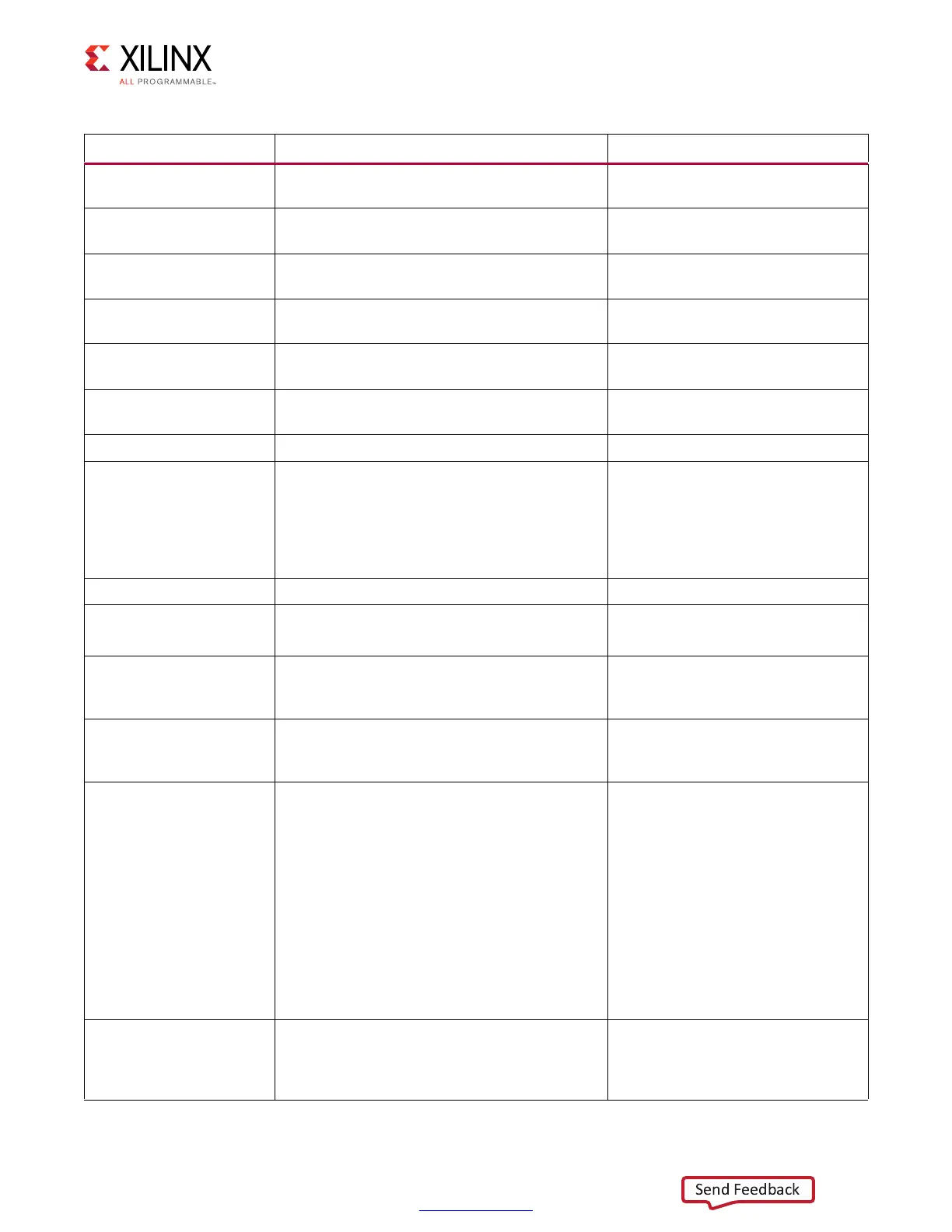

CK_WIDTH

This is the number of CK/CK# outputs to

memory.

This option is based on the selected

MIG tool configuration.

CKE_WIDTH This is the number of CKE outputs to memory.

This option is based on the selected

MIG tool configuration.

ODT_WIDTH This is the number of ODT outputs to memory.

This option is based on the selected

MIG tool configuration.

COL_WIDTH

This is the number of memory column address

bits.

This option is based on the selected

memory device.

RANK_WIDTH

This is the number of bits required to index the

RANK bus.

This parameter value is 1 for both

Single and Dual rank devices.

ROW_WIDTH

This is the DRAM component address bus

width.

This option is based on the selected

memory device.

DM_WIDTH This is the number of data mask bits. DQ_WIDTH/8

DQ_WIDTH This is the memory DQ bus width.

This parameter supports DQ widths

from 8 to a maximum of 72 in

increments of 8. The available

maximum DQ width is frequency

dependent on the selected memory

device.

DQS_WIDTH This is the memory DQS bus width. DQ_WIDTH/8

BURST_MODE This is the memory data burst length.

DDR3: “8”

DDR2: “8”

BM_CNT_WIDTH

This is the number of bits required to index a

bank machine and is given by

ceil(log

2

(nBANK_MACHS)).

ADDR_CMD_MODE

This parameter is used by the controller to

calculate timing on the memory addr/cmd bus.

This parameter should not be changed.

“1T”

ORDERING

(3)

This option reorders received requests to

optimize data throughput and latency.

“NORM”: Allows the Memory

Controller to reorder read but not

write commands to the memory.

"RELAXED": Allows the Memory

Controller to reorder commands to

the memory for maximum

efficiency. Strong ordering is not

preserved at the native interface in

this mode.

“STRICT”: Forces the Memory

Controller to execute commands in

the exact order received.

STARVE_LIMIT

This sets the number of times a read request

can lose arbitration before the request declares

itself high priority. The actual number of lost

arbitrations is STARVE_LIMIT × nBANK_MACHS.

1, 2, 3, ... 10

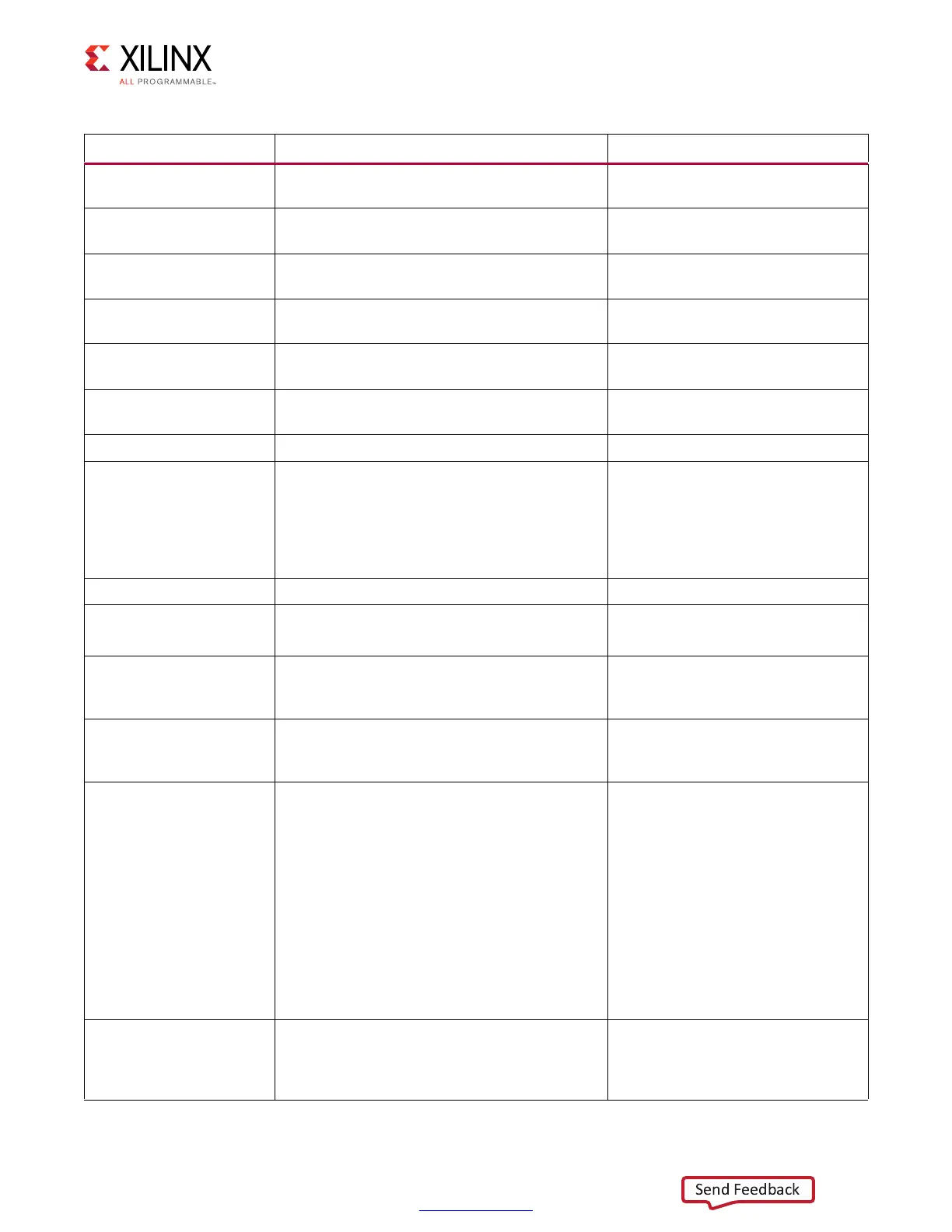

Table 1-64: 7 Series FPGA Memory Solution Configuration Parameters (Cont’d)

Parameter Description Options

Loading...

Loading...