Reference Manual ADuCM356

SEQUENCER

analog.com Rev. A | 131 of 312

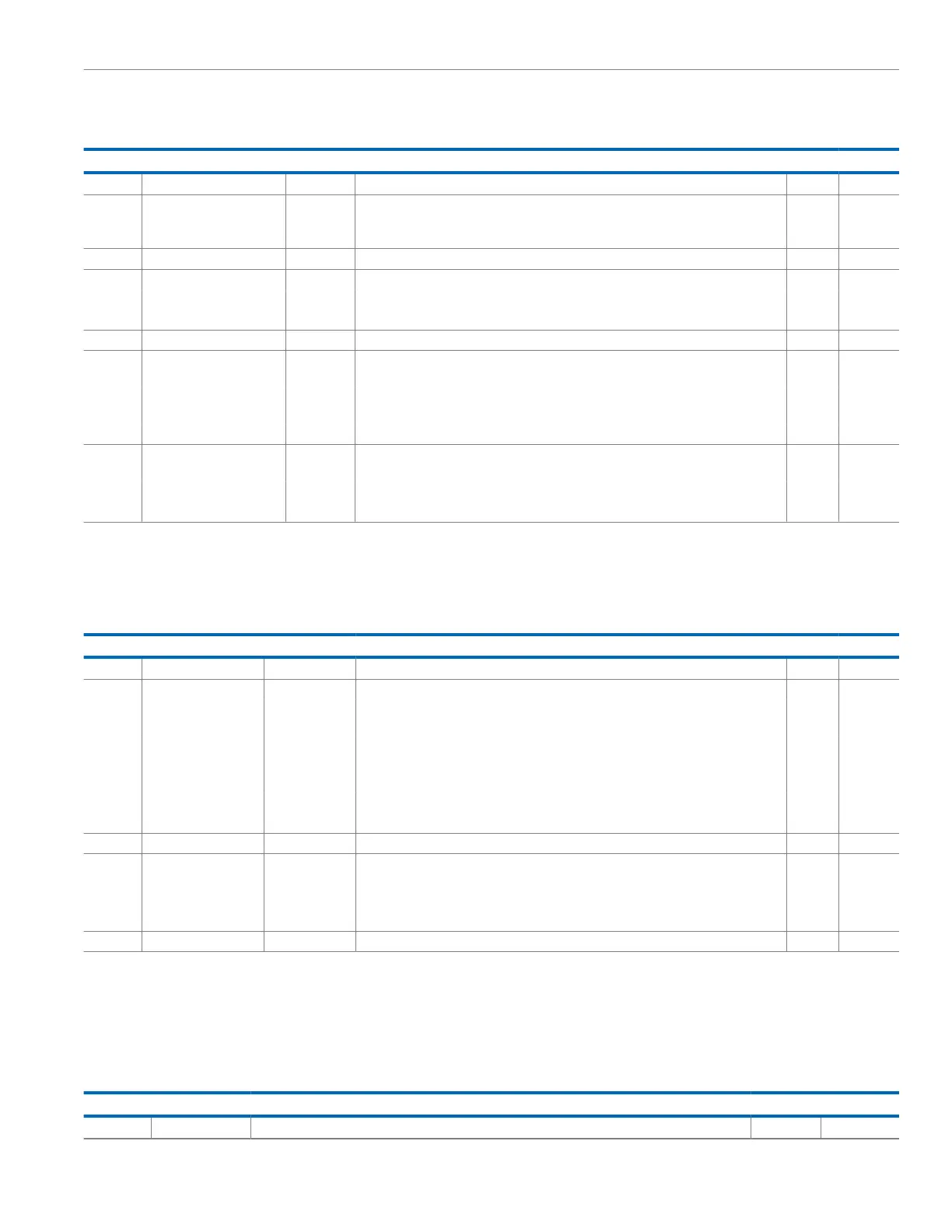

Table 155. Bit Descriptions for SEQCON Register

Bits Bit Name Settings Description Reset Access

[31:16] Reserved Reserved. 0x0 R

[15:8] SEQWRTMR Sequencer Write Commands Timer. These bits act as a clock divider affecting only the

write commands, not the wait commands. This divider is useful to reduce the code size

when generating arbitrary waveforms. The clock source for the timer is ACLK.

0x0 R/W

[7:5] Reserved Reserved. 0x0 R

4 SEQHALT Halt Sequence Debugging Feature. This bit provides a way to halt the AFE interface. 0x0 R/W

0 Normal execution.

1 Execution halted.

[3:2] Reserved Reserved. 0x0 R

1 SEQHALTFIFOEMPTY Halt Sequencer. This bit controls whether the sequencer stops when attempting to read

when the command FIFO is empty (in an underflow condition).

0x1 R/W

1 Sequencer stops if command FIFO is empty and sequencer attempts to read (in an

underflow condition).

0 Sequencer continues to attempt to read, even if the FIFO is empty.

0 SEQEN Enable Sequencer. When this bit is set to 1, the sequencer reads from the command FIFO

and executes the commands.

0x0 R/W

0 Sequencer disabled (default).

1 Sequencer enabled.

FIFO Configuration Register

Address: 0x400C2008, Reset: 0x00001010, Name: FIFOCON

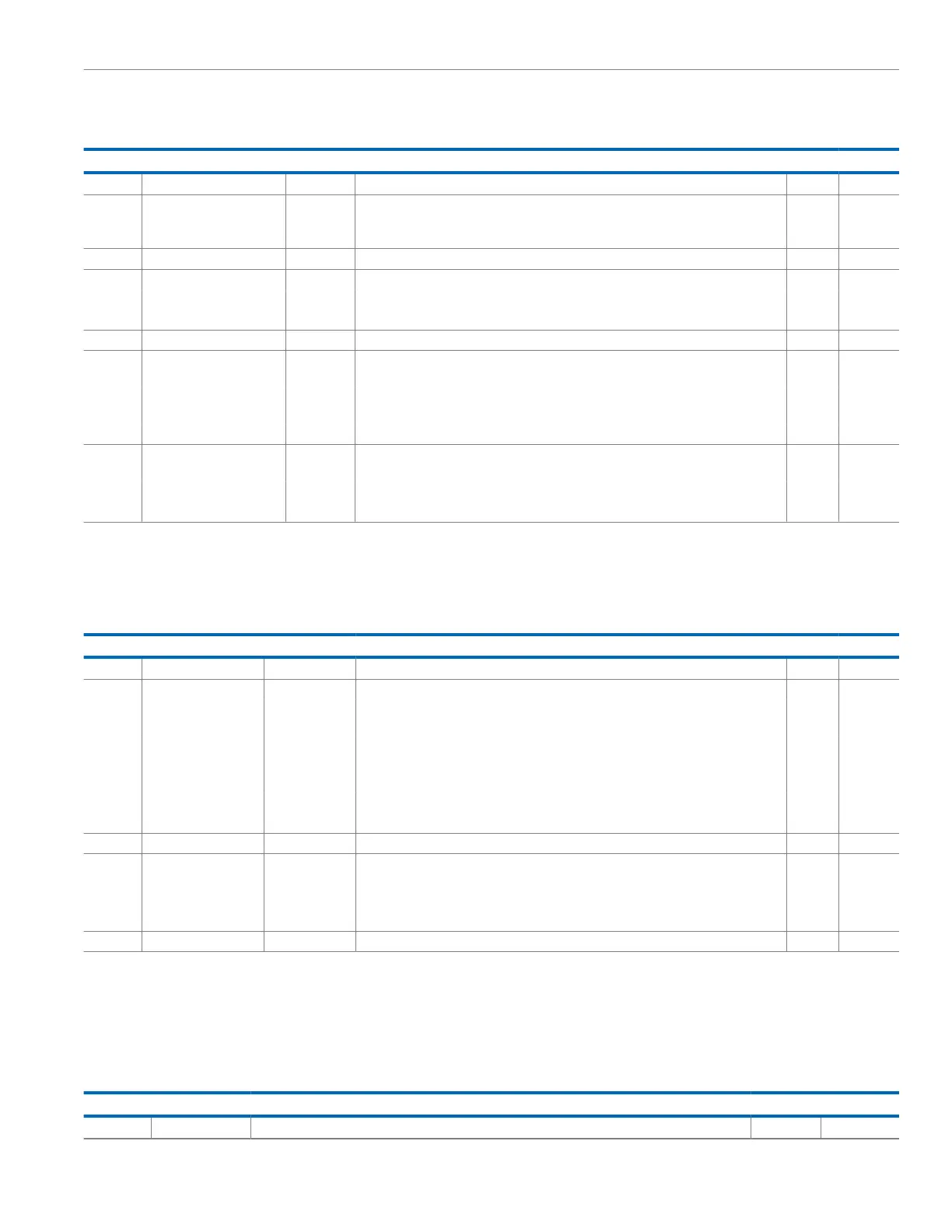

Table 156. Bit Descriptions for FIFOCON Register

Bits Bit Name Settings Description Reset Access

[31:16] RESERVED Reserved. 0x0 R

[15:13] DATAFIFOSRCSEL Data FIFO Source Select. 0x0 R/W

000, 001, 110, or

111

ADC data. The ADC data is the output of the sinc3 filter.

010 DFT data. The real part is 18 bits, and the imaginary part is 18 bits. The lowest two bits

are fractional because the ADC is 16 bits.

011 Sinc2 filter output, data is 16 bits.

100 Statistic variance output.

101 Mean result, mean is 16 bits of data.

12 Reserved Reserved. 0x1 R/W

11 DATAFIFOEN Data FIFO Enable. 0x0 R/W

0 FIFO is reset, no data transfers can take place. This setting sets the read and write

pointers to the default values (FIFO empty). The status indicates that the FIFO is empty.

1 Normal operation, the FIFO is not reset.

[10:0] Reserved Reserved. 0x0 R/W

Sequencer CRC Value Register

Address: 0x400C2060, Reset: 0x00000001, Name: SEQCRC

The SEQCRC register forms the checksum value calculated from all the commands executed by the sequencer.

Table 157. Bit Descriptions for SEQCRC Register

Bits Bit Name Description Reset Access

[31:8] Reserved Reserved. 0x0 R

Loading...

Loading...