Reference Manual ADuCM356

SEQUENCER

analog.com Rev. A | 132 of 312

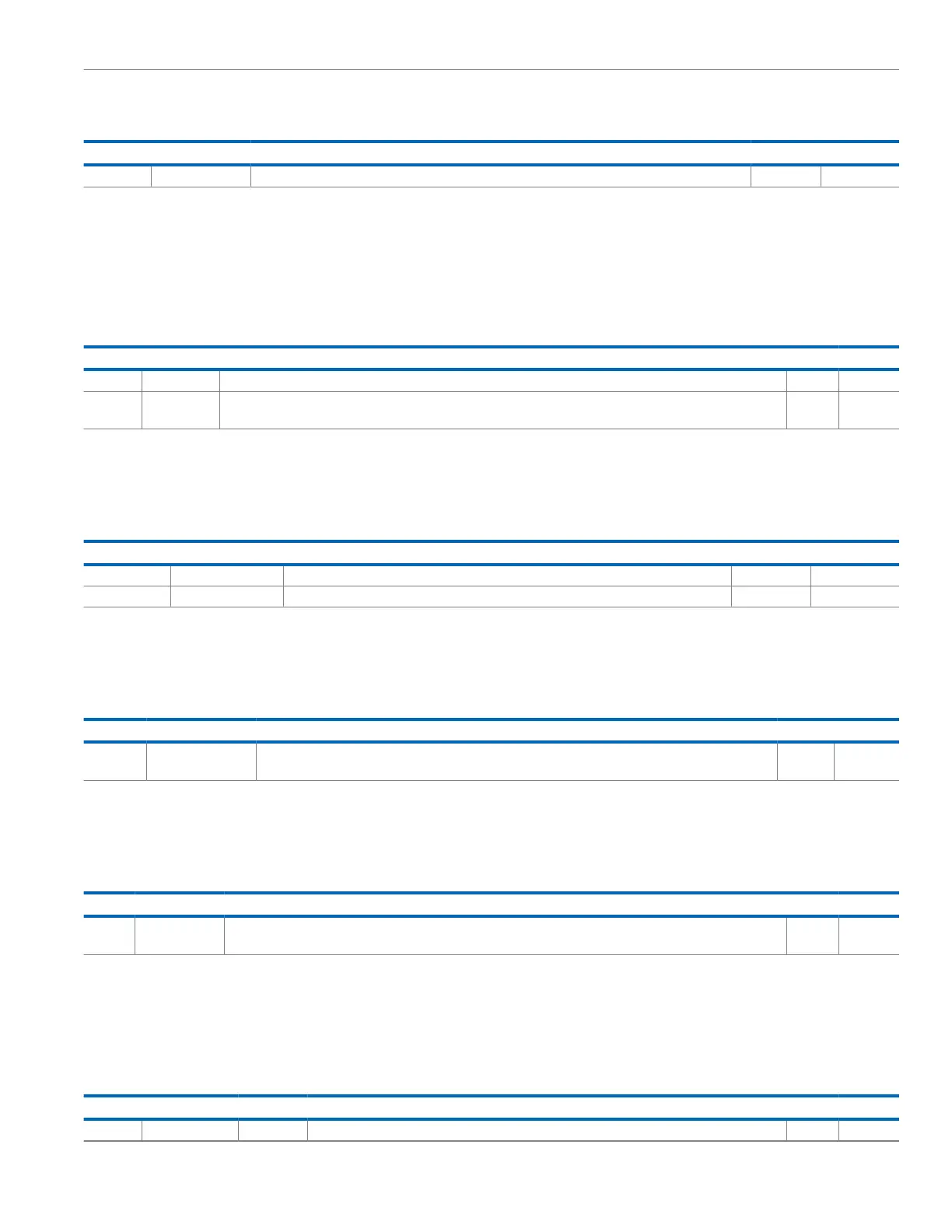

Table 157. Bit Descriptions for SEQCRC Register (Continued)

Bits Bit Name Description Reset Access

[7:0] CRC Sequencer Command CRC Value. The algorithm used is CRC-8. 0x1 R

Sequencer Command Count Register

Address: 0x400C2064, Reset: 0x00000000, Name: SEQCNT

The SEQCNT register forms the command count, which is incremented by 1 each time the sequencer executes a command. This register is not

key protected.

Table 158. Bit Descriptions for SEQCNT Register

Bits Bit Name Description Reset Access

[31:16] Reserved Reserved. 0x0 R

[15:0] Count Sequencer Command Count. This count is incremented by 1 each time the sequencer executes a command. To reset

to 0 or clear the SEQCRC register, write 1 to this register.

0x0 R/W1

Sequencer Timeout Counter Register

Address: 0x400C2068, Reset: 0x00000000, Name: SEQTIMEOUT

Table 159. Bit Descriptions for SEQTIMEOUT Register

Bits Bit Name Description Reset Access

[31:30] Reserved Reserved. 0x0 R

[29:0] Timeout Sequencer Timeout Counter Current Value. 0x0 R

Data FIFO Read Register

Address: 0x400C206C, Reset: 0x00000000, Name: DATAFIFORD

Table 160. Bit Descriptions for DATAFIFORD Register

Bits Bit Name Description Reset Access

[31:0] DATAFIFOOUT Data FIFO Read. When the data FIFO is empty, a read of this register returns 0x00000000. See Figure 32

and Figure 33 for word format details.

0x0 R

Command FIFO Write Register

Address: 0x400C2070, Reset: 0x00000000, Name: CMDFIFOWRITE

Table 161. Bit Descriptions for CMDFIFOWRITE Register

Bits Bit Name Description Reset Access

[31:0] CMDFIFOIN Command FIFO Write. If the command FIFO is written when full, the write is ignored and no current commands are

affected.

0x0 W

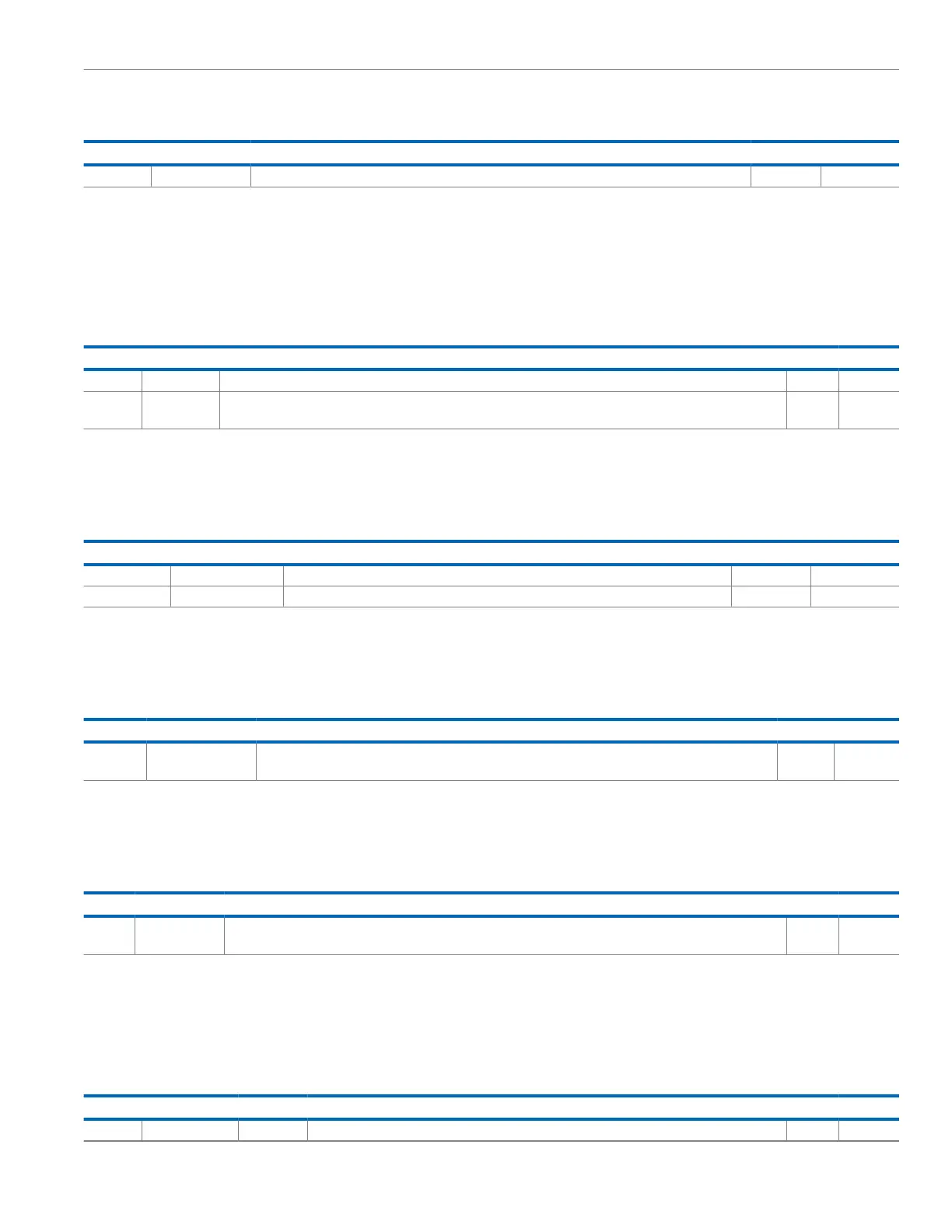

Sequencer Sleep Control Lock Register

Address: 0x400C2118, Reset: 0x00000000, Name: SEQSLPLOCK

The SEQSLPLOCK register protects the SEQTRGSLP register.

Table 162. Bit Descriptions for SEQSLPLOCK Register

Bits Bit Name Settings Description Reset Access

[31:20] Reserved Reserved. 0x0 R

Loading...

Loading...