Reference Manual ADuCM356

SEQUENCER

analog.com Rev. A | 133 of 312

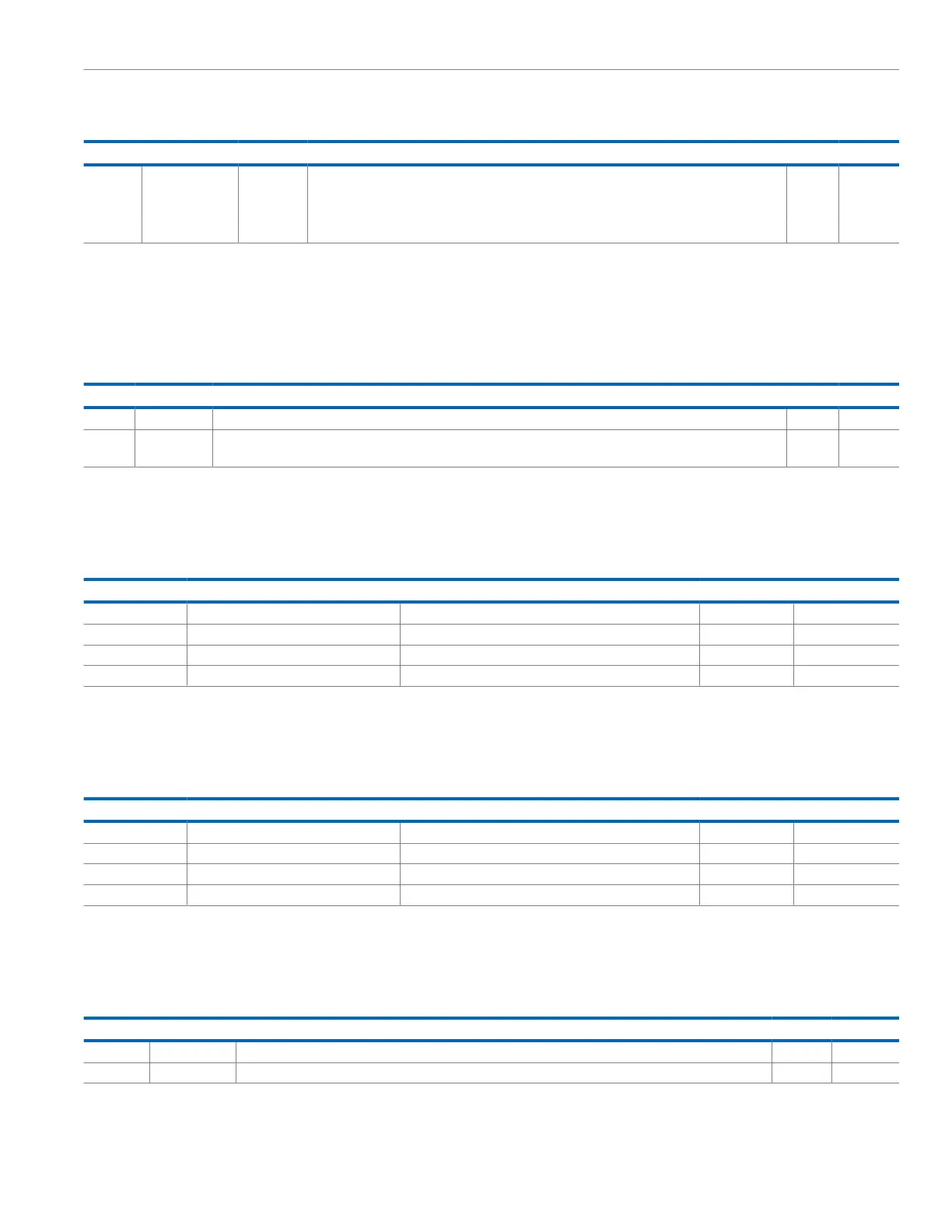

Table 162. Bit Descriptions for SEQSLPLOCK Register (Continued)

Bits Bit Name Settings Description Reset Access

[19:0] SEQ_SLP_PW SEQTRGSLP Register Password. These bits prevent the sequencer from accidentally triggering a

sleep state.

0x0 R/W

0x400C Write any value other than 0xA47E5 to lock the SEQTRGSLP register.

0xA47E5 Write this value to this register to unlock the SEQTRGSLP register.

Sequencer Trigger Sleep Register

Address: 0x400C211C, Reset: 0x00000000, Name: SEQTRGSLP

The SEQTRGSLP register is protected by the SEQSLPLOCK register.

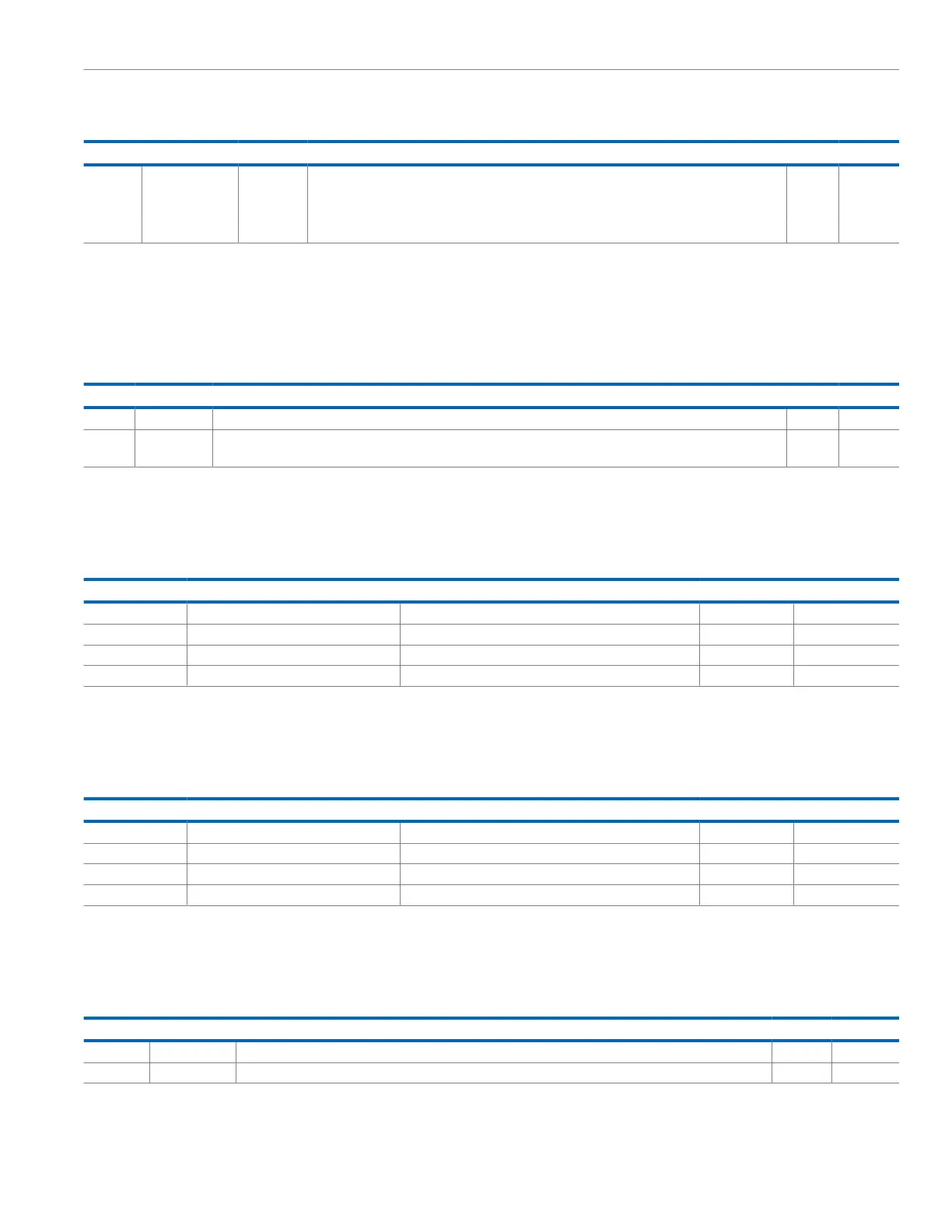

Table 163. Bit Descriptions for SEQTRGSLP Register

Bits Bit Name Description Reset Access

[31:1] Reserved Reserved. 0x0 R

0 TRGSLP Trigger Sleep by Sequencer. Write to the SEQSLPLOCK register first. Put this command at the end of a sequence. Set

this command to 1 if entering sleep at the end of a sequence.

0x0 R/W

Sequence 0 Information Register

Address: 0x400C21CC, Reset: 0x00000000, Name: SEQ0INFO

Table 164. Bit Descriptions for SEQ0INFO Register

Bits Bit Name Description Reset Access

[31:27] Reserved Reserved. 0x0 R

[26:16] SEQ0INSTNUM SEQ0 Instruction Number. 0x0 R/W

[15:11] Reserved Reserved. 0x0 R

[10:0] SEQ0STARTADDR SEQ0 Start Address. 0x0 R/W

Sequence 2 Information Register

Address: 0x400C21D0, Reset: 0x00000000, Name: SEQ2INFO

Table 165. Bit Descriptions for SEQ2INFO Register

Bits Bit Name Description Reset Access

[31:27] Reserved Reserved. 0x0 R

[26:16] SEQ2INSTNUM SEQ2 Instruction Number. 0x0 R/W

[15:11] Reserved Reserved. 0x0 R

[10:0] SEQ2STARTADDR SEQ2 Start Address. 0x0 R/W

Command FIFO Write Address Register

Address: 0x400C21D4, Reset: 0x00000000, Name: CMDFIFOWADDR

Table 166. Bit Descriptions for CMDFIFOWADDR Register

Bits Bit Name Description Reset Access

[31:11] Reserved Reserved. 0x0 R

[10:0] WADDR Write Address. These bits are the address in SRAM in which the command is stored. 0x0 R/W

Loading...

Loading...