Reference Manual ADuCM356

AFE INTERRUPTS

analog.com Rev. A | 141 of 312

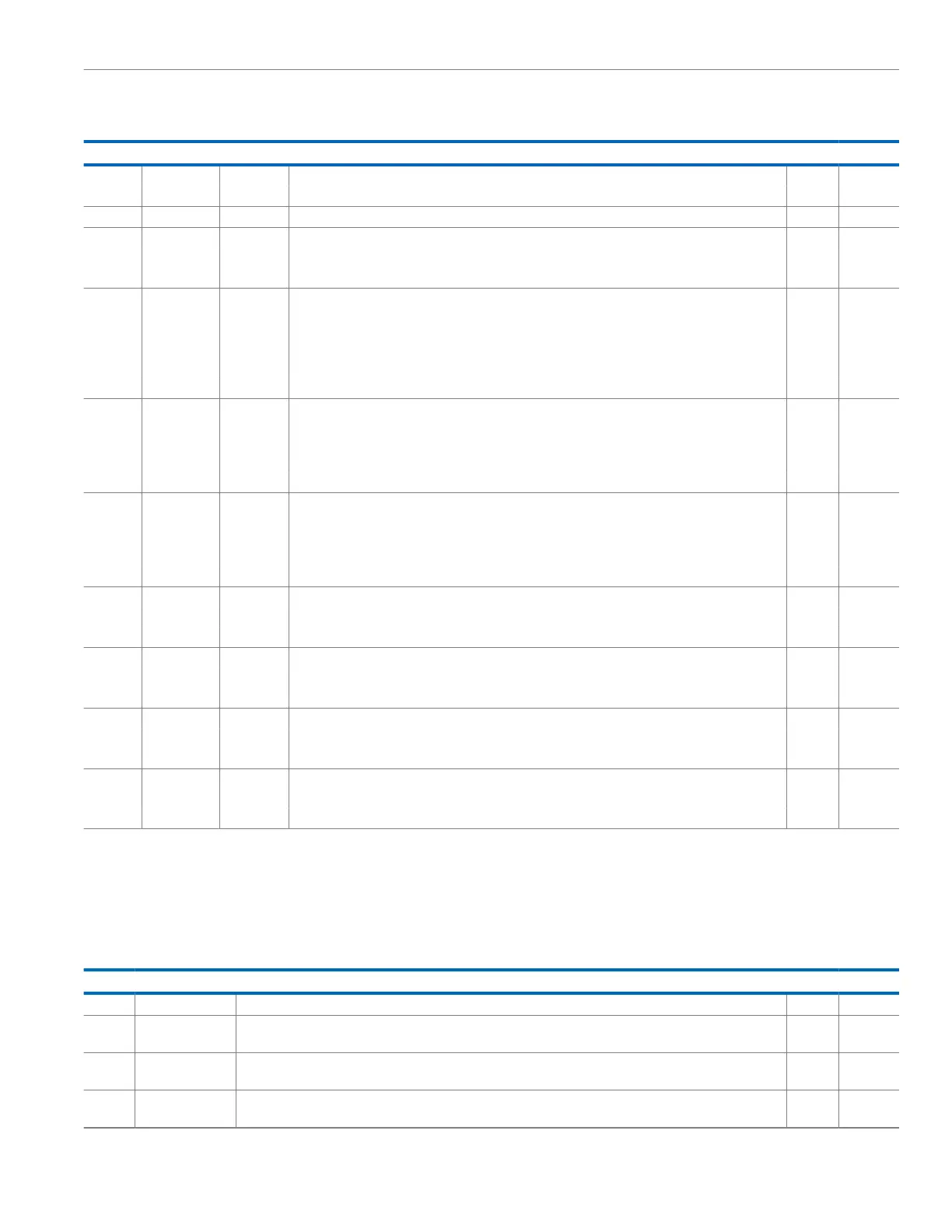

Table 178. Bit Descriptions for INTCFLAG0 and INTCFLAG1 Registers (Continued)

Bits Bit Name Settings Description Reset Access

0 Interrupt not asserted.

1 Interrupt asserted.

8 Reserved Reserved. 0x0 R

7 FLAG7 Mean IRQ Status. 0x0 R

0 Interrupt not asserted.

1 Interrupt asserted.

6 FLAG6 ADC Delta Fail IRQ Status. When this bit is set, it indicates that the difference between two consecutive

ADC results is greater than the value specified by the ADCDELTA register. If this bit is clear, it indicates

that no difference between two consecutive ADC values greater than the limit is detected since the last

time this bit was cleared.

0x0 R

0 Interrupt not asserted.

1 Interrupt asserted.

5 FLAG5 ADC Maximum Fail IRQ Status. When this bit is set, it indicates that an ADC result is above the

maximum value specified by the ADCMAX register. If this bit is clear, it indicates that no ADC value

above the maximum is detected.

0x0 R

0 Interrupt not asserted.

1 Interrupt asserted.

4 FLAG4 ADC Minimum Fail IRQ Status. When this bit is set, it indicates that an ADC result is below the minimum

value as specified by the ADCMIN register. If this bit is clear, it indicates that no ADC value below the

limit is detected since the last time this bit was cleared.

0x0 R

0 Interrupt not asserted.

1 Interrupt asserted.

3 FLAG3 Temperature Result IRQ Status. 0x0 R

0 Interrupt not asserted.

1 Interrupt asserted.

2 FLAG2 Sinc2 Filter Result Ready IRQ Status. 0x0 R

0 Interrupt not asserted.

1 Interrupt asserted.

1 FLAG1 DFT Result IRQ Status. 0x0 R

0 Interrupt not asserted.

1 Interrupt asserted.

0 FLAG0 ADC Result IRQ Status. 0x0 R

0 Interrupt not asserted.

1 Interrupt asserted.

Analog Generation Interrupt Register

Address: 0x400C209C, Reset: 0x00000010, Name: AFEGENINTSTA

The AFEGENINTSTA register provides custom interrupt generation. Writing to this register is only possible using the sequencer.

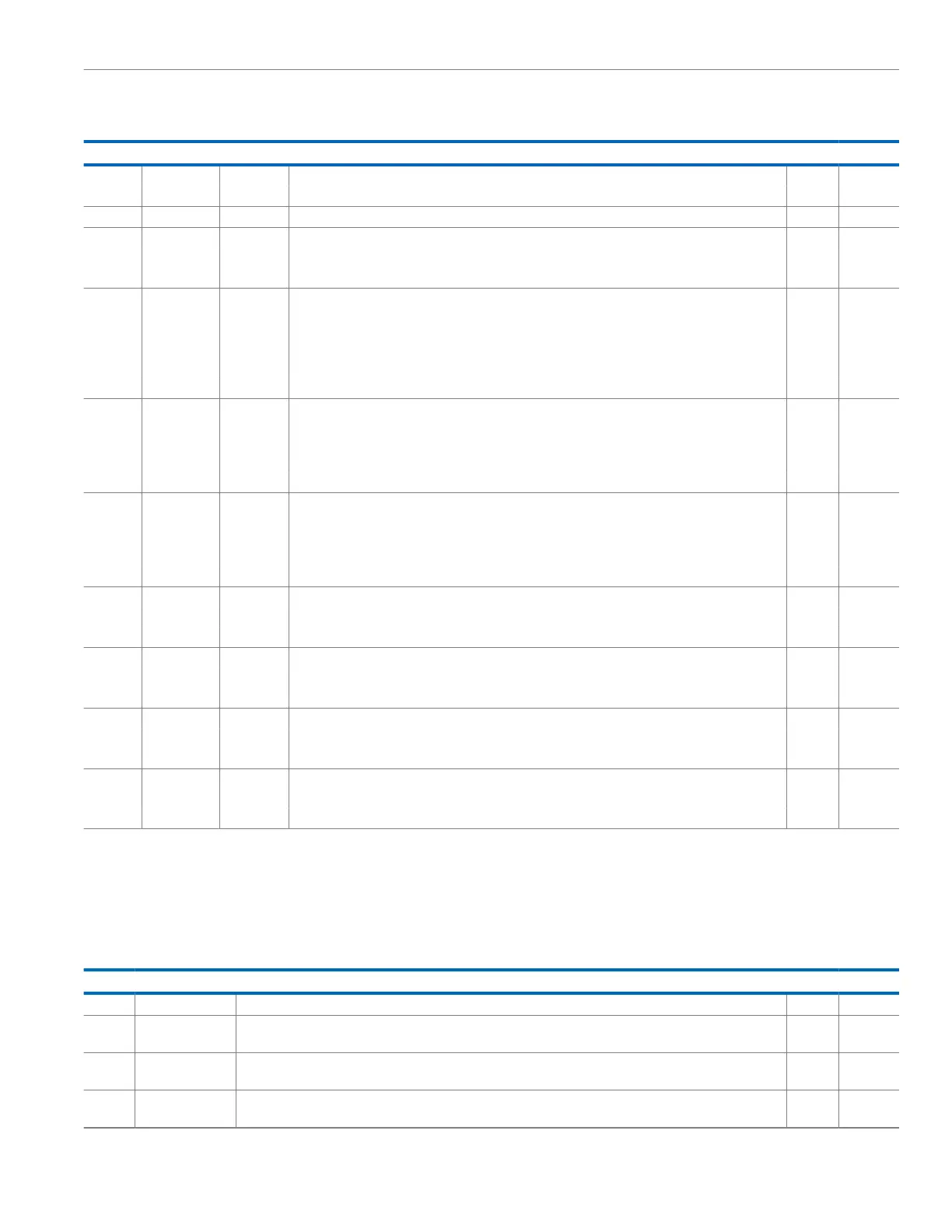

Table 179. Bit Descriptions for AFEGENINTSTA Register

Bits Bit Name Description Reset Access

[31:4] Reserved Reserved. 0x1 R

3 CUSTOMINT3 General-Purpose Custom Interrupt 3. Set this bit manually using the sequencer program. Write 1 to this bit to trigger

an interrupt.

0x0 R/W1C

2 CUSTOMINT2 General-Purpose Custom Interrupt 2. Set this bit manually using the sequencer program. Write 1 to this bit to trigger

an interrupt.

0x0 R/W1C

1 CUSTOMINT1 General-Purpose Custom Interrupt 1. Set this bit manually using the sequencer program. Write 1 to this bit to trigger

an interrupt.

0x0 R/W1C

Loading...

Loading...