Reference Manual ADuCM356

DMA CONTROLLER

analog.com Rev. A | 165 of 312

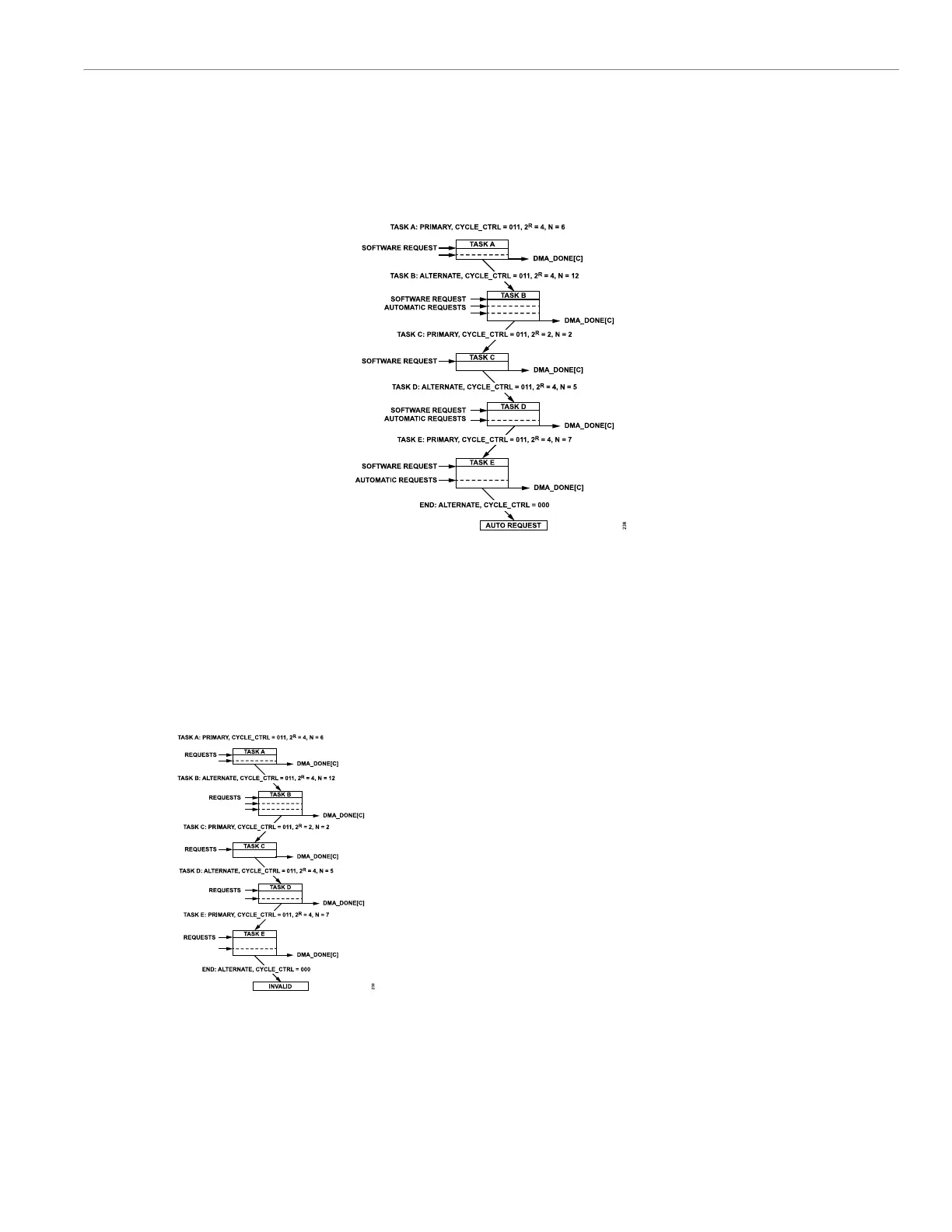

Software Ping Pong DMA Transfer

(CHNL_CFG, Bits[2:0] = 011)

In this mode, if the DMA request comes from the software, a

request is generated automatically after each arbitration cycle until

the completion of primary or alternate descriptor tasks. This final

descriptor must use an autorequest transfer type. This mode is

shown in Figure 44.

Figure 44. Software Ping Pong DMA Transfer

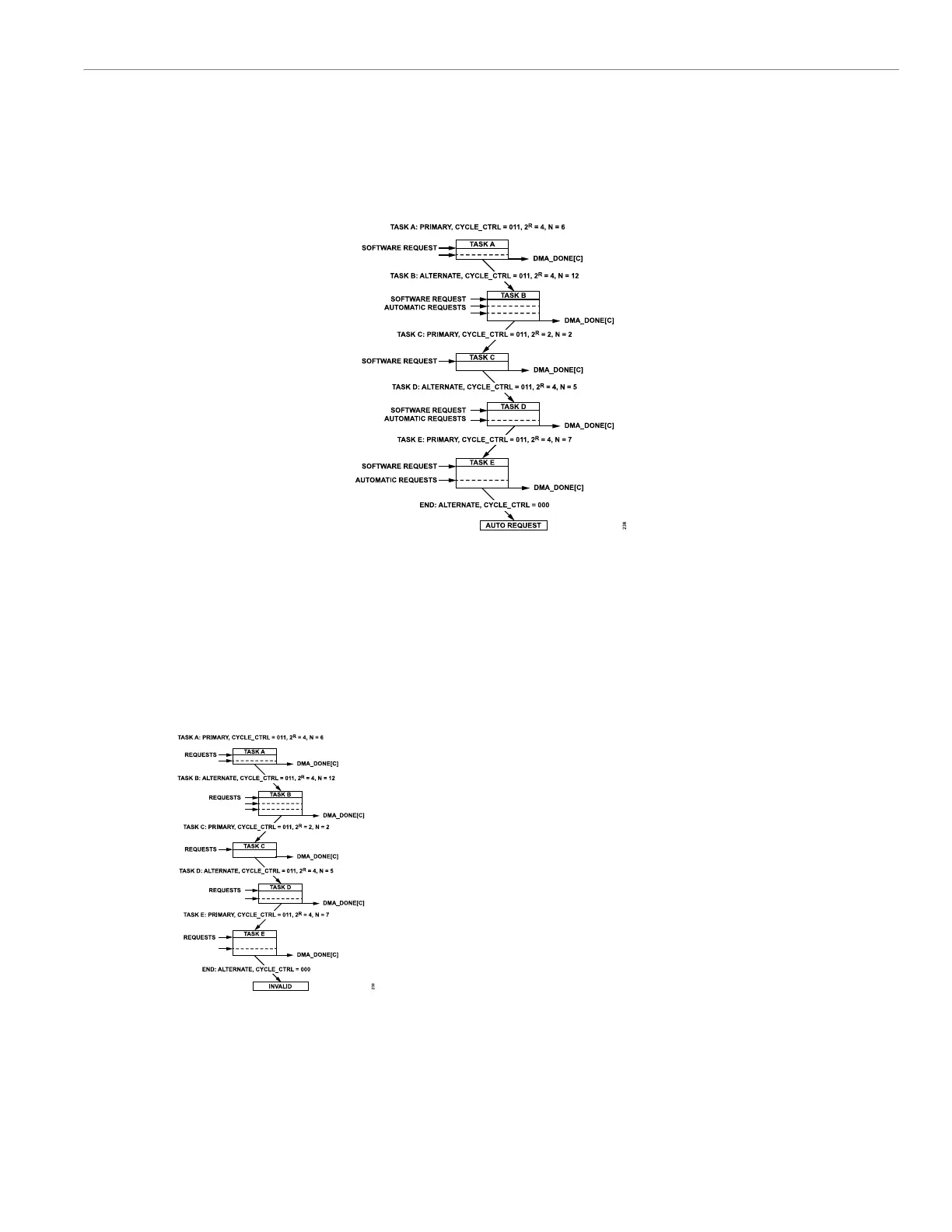

Peripheral Ping Pong DMA Transfer

(CHNL_CFG, Bits[2:0] = 011)

In this mode, if the DMA request is from a peripheral, the peripheral

must send DMA requests after every data transfer to complete

primary or alternate descriptor tasks and the final descriptor must

be programmed to use a basic transfer type. This mode is shown in

Figure 45.

Figure 45. Peripheral Ping Pong DMA Transfer

Memory Scatter Gather (CHNL_CFG, Bits[2:0] =

100 or 101)

In memory scatter gather mode, the controller must be configured

to use both the primary and alternate data structures. The controller

uses the primary data structure to program the control configuration

for the alternate data structure. The alternate data structure is used

for actual data transfers, which are similar to an autorequest DMA

transfer. The controller arbitrates after every primary transfer. The

controller requires only one request to complete the entire transfer.

This mode is used when performing multiple memory to memory

copy tasks. The MCU can configure all of the tasks simultaneously

and does not need to intervene in between each task. The control-

ler generates the corresponding DMA channel interrupt in the NVIC

when the entire scatter gather transaction completes using a basic

cycle.

In memory scatter gather mode, the controller receives an initial

request and then performs four DMA transfers using the primary

data structure to program the control structure of the alternate data

structure. After these transfers are completed, the controller starts

a DMA cycle using the alternate data structure. After the cycle com-

pletes, the controller performs another four DMA transfers using

the primary data structure. The controller continues to alternate

between using the primary and alternate data structures until the

processor configures the alternate data structure for a basic cycle

or the DMA reads an invalid data structure.

Table 194 details the fields of the CHNL_CFG memory location

for the primary data structure, which must be programmed with

constant values for the memory scatter gather mode. This mode is

also shown in Figure 46.

Loading...

Loading...