Reference Manual ADuCM356

SERIAL PERIPHERAL INTERFACES

analog.com Rev. A | 239 of 312

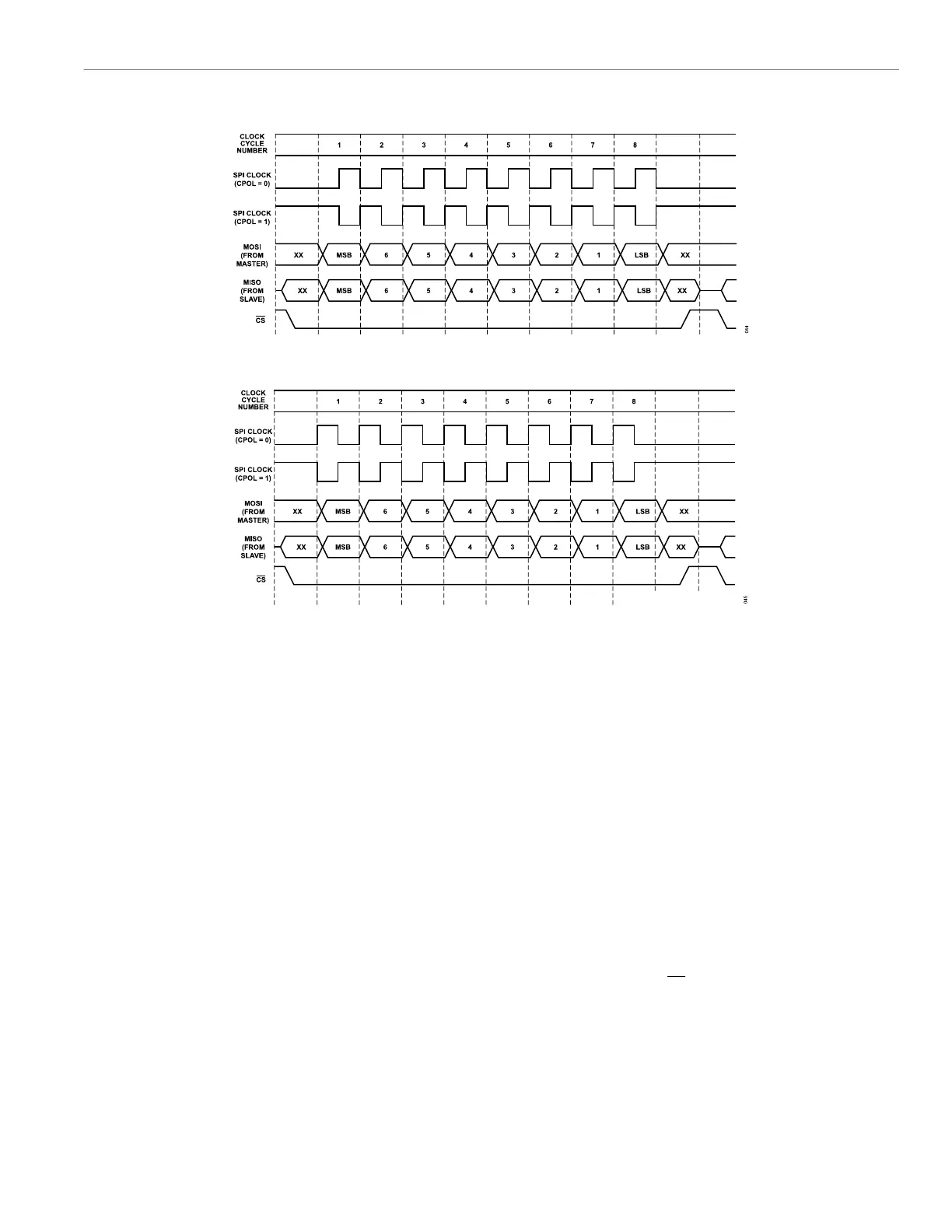

Figure 61. SPI Transfer Protocol, CPHA = 0

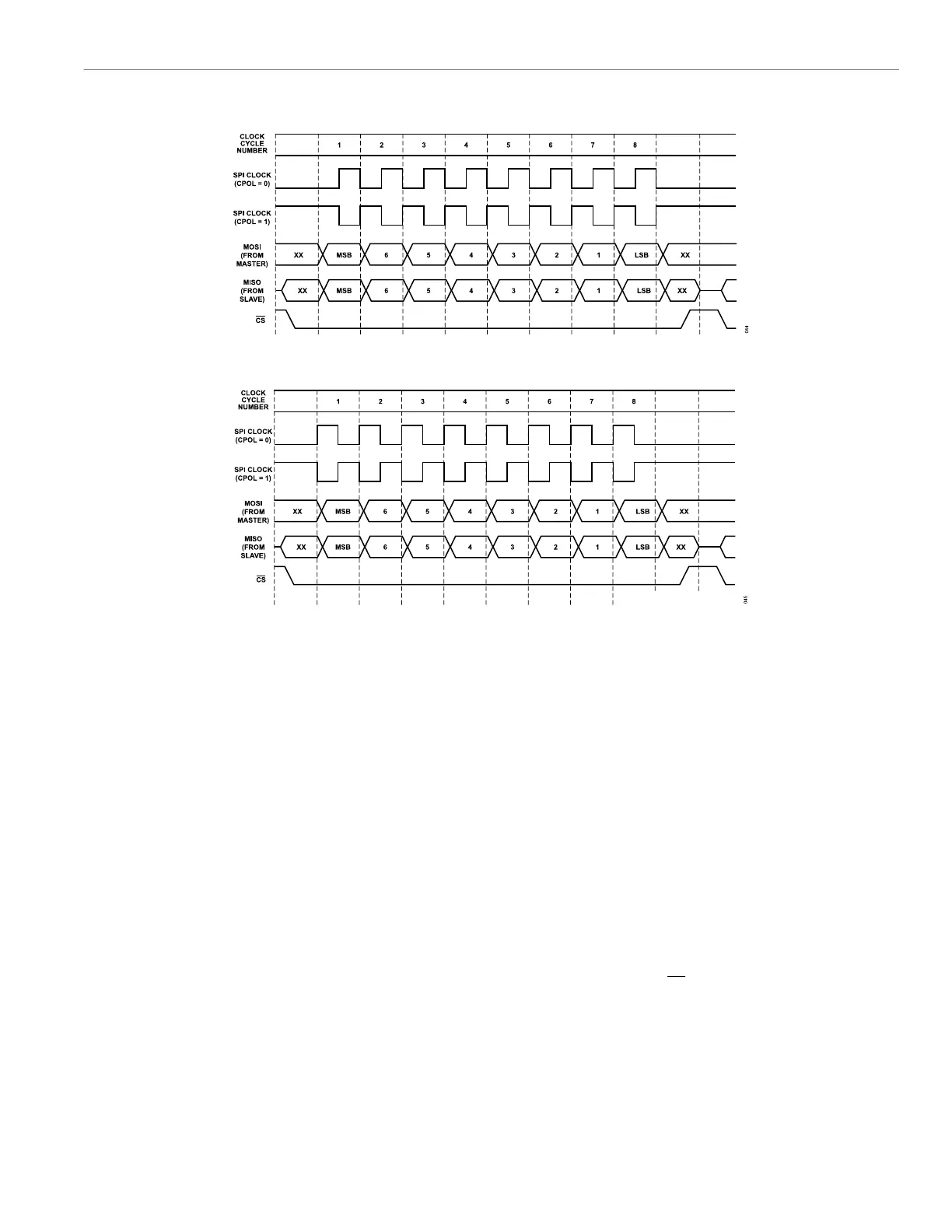

Figure 62. SPI Transfer Protocol, CPHA = 1

Transfers in Target Mode

In target mode, a transfer is initiated by the assertion of the chip

select of the device. Though the initiator can support up to four

chip select output lines, only one chip select input is used in target

mode. The device as a target transmits and receives 8-bit data until

the transfer is concluded by the deassertion of chip select. The SPI

transfer protocol diagrams in Figure 61 and Figure 62 illustrate the

data transfer protocol for the SPI, and the effects of SPIx_CTL, Bit

2 and SPIx_CTL, Bit 3 on that protocol. The chip select must not be

tied to the ground.

SPI Data Underrun and Overflow

If the transmit zeros enable bit (SPIx_CTL, Bit 7) is cleared, the last

byte from the previous transmission is shifted out when a transfer is

initiated with no valid data in the FIFO. If SPIx_CTL, Bit 7 is set to

1, 0s are transmitted when a transfer is initiated with no valid data

in the FIFO. If the receive overflow overwrite enable bit (SPIx_CTL,

Bit 8) is set, and there is no space left in the FIFO, the valid data

in the receive FIFO is overwritten by the new serial byte received. If

SPIx_CTL, Bit 8 is cleared, and there is no space left in the FIFO,

the new serial byte received is discarded. When SPIx_CTL, Bit 8

is set, the contents of the SPI receive FIFO are undefined, and its

contents must be discarded by user code.

Full Duplex Operation

Simultaneous reads and writes are supported on the SPI. When im-

plementing full duplex transfers in initiator mode, use the following

procedure:

1. Initiate a transfer sequence via a transmit on the P0.1/

SPI0_MOSI pin and the P1.3/SPI1_MOSI pin. Set SPIx_CTL,

Bit 6 = 1. If interrupts are enabled, interrupts are triggered when

a transmit interrupt occurs but not when a byte is received.

2. If using interrupts, the SPI transmit interrupt indicated by

SPIx_STAT, Bit 5 or the transmit FIFO underrun interrupt

(SPIx_STAT, Bit 4) is asserted approximately three to four SPI

clock periods into the transfer of the first byte. If necessary,

reload a byte into the transmit FIFO by writing to the SPIx_TX

register.

3. The first byte received via the MISO pin does not update the

receive FIFO status bits (SPIx_FIFO_STAT, Bits[11:8]) until 12

SPI clock periods after CS goes low. Therefore, two transmit

interrupts can occur before the first receive byte is ready to be

processed.

4. After the last transmit interrupt occurs, it may be necessary to

read two more bytes. It is recommended that SPIx_FIFO_STAT,

Bits[11:8] be polled outside of the SPI interrupt handler after the

last transmit interrupt is handled.

Loading...

Loading...