Reference Manual ADuCM356

CYCLIC REDUNDANCY CHECK

analog.com Rev. A | 307 of 312

DMA Access Steps

The CRC accelerator block supports software DMA. To access the

DMA, take the following steps:

1. Program the POLY register with the required polynomial left

justified, as shown in the Polynomial section.

2. Program the result register with an initial seed value. The seed

must be justified and written to the result register, as detailed in

the Polynomial section.

3. Enable accelerator function by writing to the CTL register.

Note that the following steps require a single write to the CTL

register:

a. Set the EN bit high.

b. Modify the W16SWP, BYTMIRR, and BITMIRR bits in the

CTL register, which configure the application with different

mirroring options. For more information, see the Mirroring

Options section.

c. Set or reset the LSBFIRST bit to indicate LSB first or MSB

first CRC calculation.

The DMA can start sending CRC data by writing to the IPDATA

register. The CRC accelerator block continues to calculate the

CRC as long as the data is written to IPDATA.

4. Set up the DMA channels using the required parameters:

DST_END_PTR is the IPDATA register address, data size is

the word, destination no increment is the channel used. For

more information about programming the DMA, see the DMA

Controller section. A DMA_DONE interrupt signal of the DMA

channel indicates the completion of data transfer to the CRC

block.

5. Repeat Step 1 to Step 4 until all the data has been sent to the

accelerator block.

6. Read the result register. This register contains the x-bit result in

x MSB bits for MSB first and in x LSB bits for LSB first CRC

calculations.

7. Calculate CRC on the next data block. To calculate the CRC on

the next block of data, repeat Step 1 to Step 5.

8. Disable the CRC accelerator block by clearing the EN bit in CTL

to ensure that the block is in a low-power state.

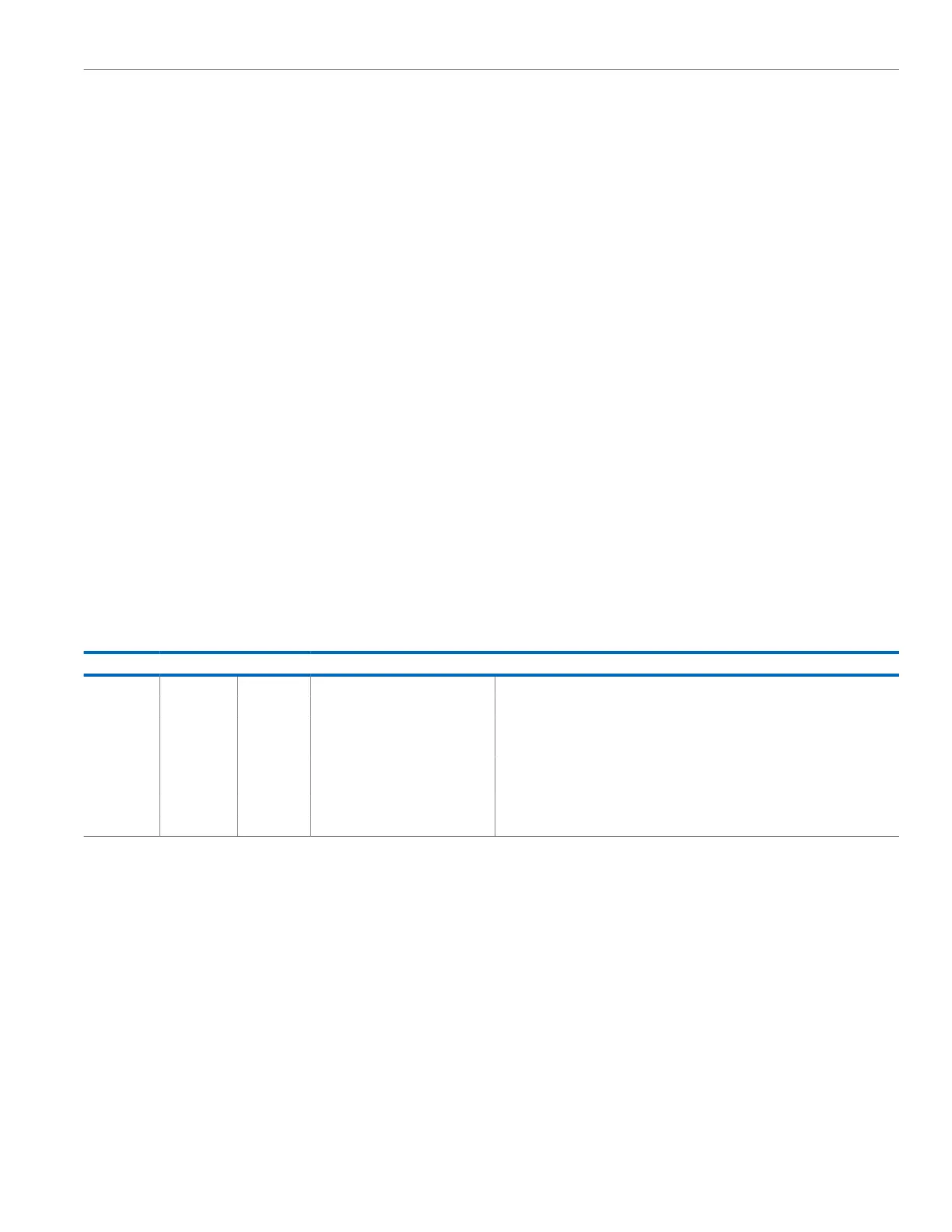

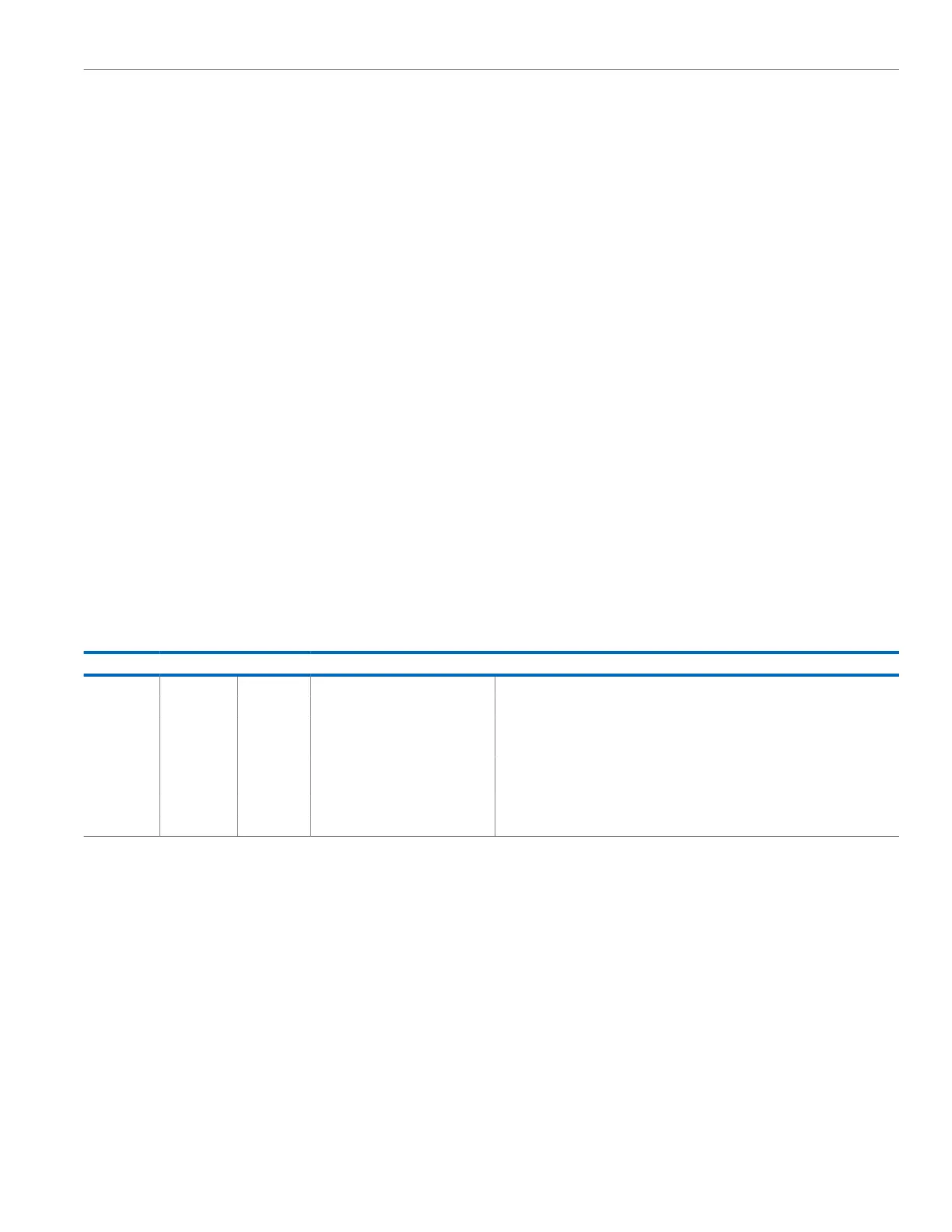

Mirroring Options

The W16SWP, BITMIRR, and BYTMIRR bits in CTL determine the

sequence of the bits in which the CRC is calculated. Table 403

details all of the mirroring options used within the CRC block for a

32-bit polynomial.

DIN, Bits[31:0] is the data being written to the IPDATA register,

and CIN, Bits[31:0] is the data after the mirroring of the data. The

serial engine calculates CIN, Bits[31:0] starting with the MSB bit

and ending with LSB bit in sequence (CIN, Bit 31 to CIN, Bit 0 in

descending order).

Table 403. Mirroring Options for 32-Bit Input Data with 32-Bit Polynomial

W16SWP BYTMIRR BITMIRR Input Data DIN, Bits[31:0] CRC Input Data (CIN, Bits[31:0])

0 0 0 DIN, Bits[31:0] CIN, Bits[31:0] = DIN, Bits[31:0]

0 0 1 DIN, Bits[31:0] CIN, Bits[31:0] = DIN, Bits[31:24]; DIN, Bits[23:16]; DIN, Bits[15:8]; DIN, Bits[7:0]

0 1 0 DIN, Bits[31:0] CIN, Bits[31:0] = DIN, Bits[31:24]; DIN, Bits[23:16]; DIN, Bits[15:8]; DIN, Bits[7:0]

0 1 1 DIN, Bits[31:0] CIN, Bits[31:0] = DIN, Bits[31:24]; DIN, Bits[23:16]; DIN, Bits[15:8]; DIN, Bits[7:0]

1 0 0 DIN, Bits[31:0] CIN, Bits[31:0] = DIN, Bits[31:16]; DIN, Bits[15:0]

1 0 1 DIN, Bits[31:0] CIN, Bits[31:0] = DIN, Bits[31:24]; DIN, Bits[23:16]; DIN, Bits[15:8]; DIN, Bits[7:0]

1 1 0 DIN, Bits[31:0] CIN, Bits[31:0] = DIN, Bits[31:24]; DIN, Bits[23:16]; DIN, Bits[15:8]; DIN, Bits[7:0]

1 1 1 DIN, Bits[31:0] CIN, Bits[31:0] = DIN, Bits[31:24]; DIN, Bits[23:16]; DIN, Bits[15:8]; DIN, Bits[7:0]

Loading...

Loading...