Reference Manual ADuCM356

ADC CIRCUIT

analog.com Rev. A | 56 of 312

Sinc3 Filter

The input is the raw ADC codes at a rate of 800 kHz if the 16 MHz

oscillator is selected on the analog die, or 1.6 MHz if the 32 MHz

oscillator is selected on the analog die.

To enable the sinc3 filter, ensure that ADCFILTERCON, Bit 6 =

0. The filter decimation rate is programmable. The recommended

decimation or oversampling rate (OSR) is 4. The OSR is controlled

by ADCFILTERCON, Bits[13:12]. The input rate is 200 kSPS in

normal mode if the 16 MHz oscillator is selected, and 400 kSPS in

high-speed mode if the 32 MHz oscillator is selected.

If selected, the sinc3 filter output can be read via the ADCDAT

register. When changing the ADC input channels or when changing

the ADC update rates via ADCFILTERCON, the user must reset the

sinc3 filter. If sinc3 filter is not reset, ADC samples with the new

settings are inaccurate.

The following are example instructions:

pADI_AFE->AFECON &= (~(BITM_AFE_AFECON_ADCCONV►

EN)); // Clear AFECON[8]

pADI_AFE->AFECON |= BITM_AFE_AFECON_ADCCONV►

EN; // Set AFECON[8]

Sinc2 Filter

The input is the gain or offset adjusted codes from the sinc3 filter

or from the ADC. The input rate is 800 kSPS if coming directly

from the ADC when the 16 MHz oscillator is selected, 1.6 MSPS

if coming directly from the ADC when the 32 MHz oscillator is

selected, and 400 kSPS or 160 kSPS if coming directly from the

sinc3 filter output.

To enable the sinc2 filter, set AFECON, Bit 16 = 1. The output

rate from the sinc2 filter is programmable via ADCFILTERCON,

Bits[11:8]. The decimation rate is a minimum of divide by 22 to a

maximum of divide by 1333. If selected, the sinc2 filter output can

be read via the SINC2DAT register.

When changing ADC input channels, restarting the ADC, or chang-

ing the ADC update rates via the ADCFILTERCON register, reset

the sinc2 filter. If the sinc2 filter is not reset, the ADC samples with

the new settings are inaccurate.

The following are example instructions:

pADI_AFE->AFECON &= (~(BITM_AFE_AFE►

CON_SINC2EN)); // Clear AFECON[16]

pADI_AFE->AFECON |= BITM_AFE_AFE►

CON_SINC2EN; // Set AFECON[16]

Power Supply Rejection Filter (50 Hz or 60 Hz

Mains Filter)

To enable the 50 Hz or 60 Hz notch filter for filtering mains noise,

clear ADCFILTERCON, Bit 4 = 0 and set AFECON, Bit 16 = 1.

The input is the sinc2 filter output. The input rate is dependent on

the sinc3 and sinc2 settings. If selected, the power supply rejection

filter output can be read via the SINC2DAT register. Table 53

describes the digital filter settings that support simultaneous 50 Hz

or 60 Hz mains rejection.

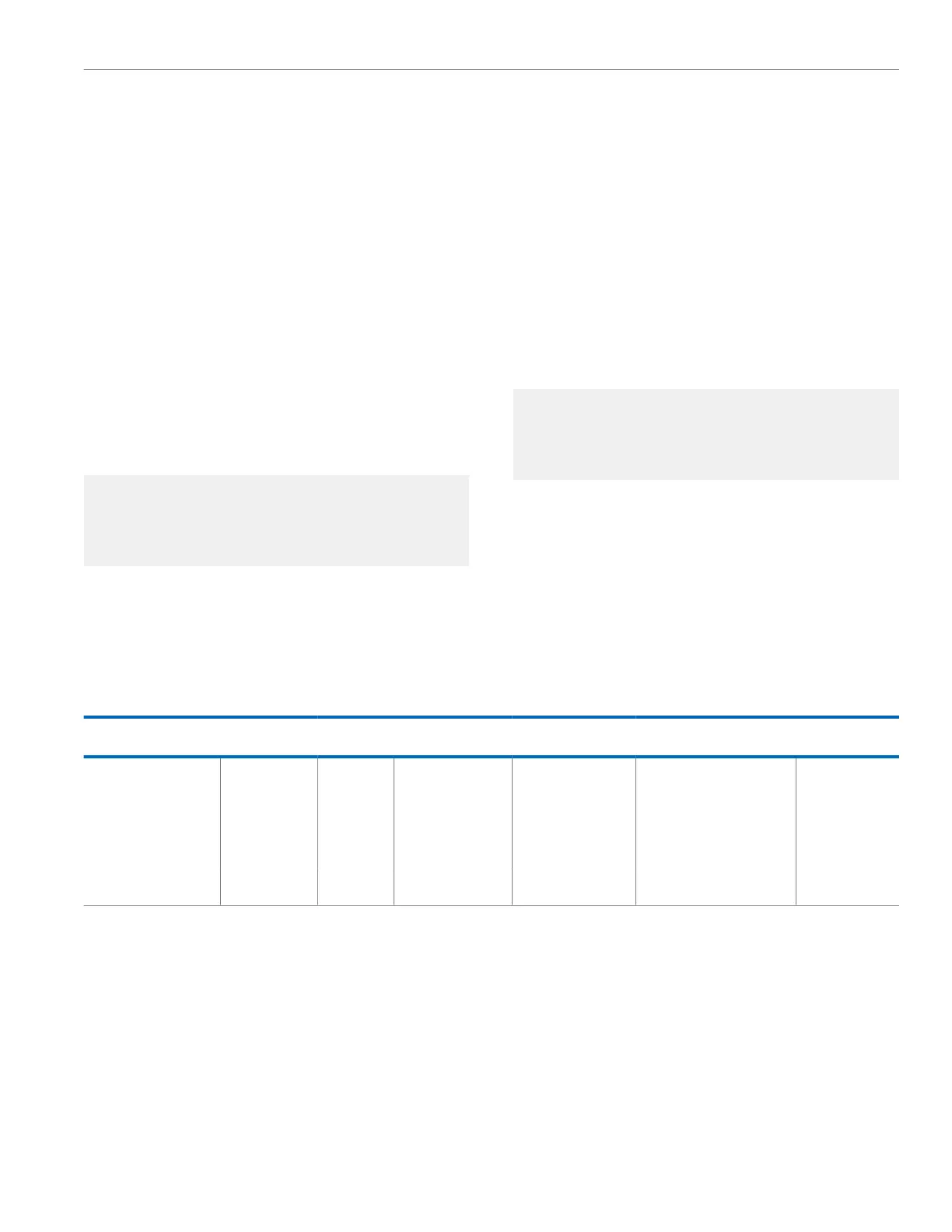

Table 53. Digital Filter Settings for 50 Hz or 60 Hz Mains Rejection

ADCFILTERCON

Bits[13:8] Value

Power Mode

(PMBW Bit 0)

ADC Clock

Setting (MHz)

Sinc3 Oversampling

Setting

Sinc2 Oversampling

Setting

Final ADC Output Update

Rate in Samples per Second

Filter Settling Time

(ms)

0b000011 0 (low-power

mode)

16 5 178 900 37

0b100111 0 (low-power

mode)

16 2 667 600 37

0b101011 0 (low-power

mode)

16 2 1333 300 37

0b101011 1 (high-power

mode)

32 2 1333 600 37

Gain Correction

The gain correction of the sinc2 filter and power supply rejection

filter occurs in the gain correction block. The block is automatically

enabled in hardware, and no user configuration is required.

Digital DFT

The DFT accelerator is intended for use during impedance meas-

urements. To enable the DFT block, set AFECON, Bit 15 = 1.

The input can be the raw ADC results, sinc2 output, sinc3 output

(ADCDAT register), or the power supply filter output (SINC2DAT

register).

Configure the DFT using DFTCON, Bits[21:20]. The DFT outputs

a complex number (real and imaginary terms) that represents the

overall DFT result for the selected number of ADC samples of the

applied AC waveform. See the DFT Result, Real Part Register

section and the DFT Result, Imaginary Part Register section. The

number of samples used by the DFT is configurable via DFTCON,

Bits[7:4] (see the AFE DSP Configuration Register section). A

Hanning window (raised cosine window) option is available. To

enable the Hanning window, set DFTCON, Bit 0 to 1. If enabled,

values outside the selected interval are set to 0. It is recommended

to enable the Hanning window.

Loading...

Loading...