Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 491

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

A working example design simulation completes memory initialization and runs traffic in

response to the test bench stimulus. Successful completion of memory initialization and

calibration results in the assertion of the init_calib_complete signal. When this signal

is asserted, the Traffic Generator takes control and begins executing writes and reads

according to its parameterization.

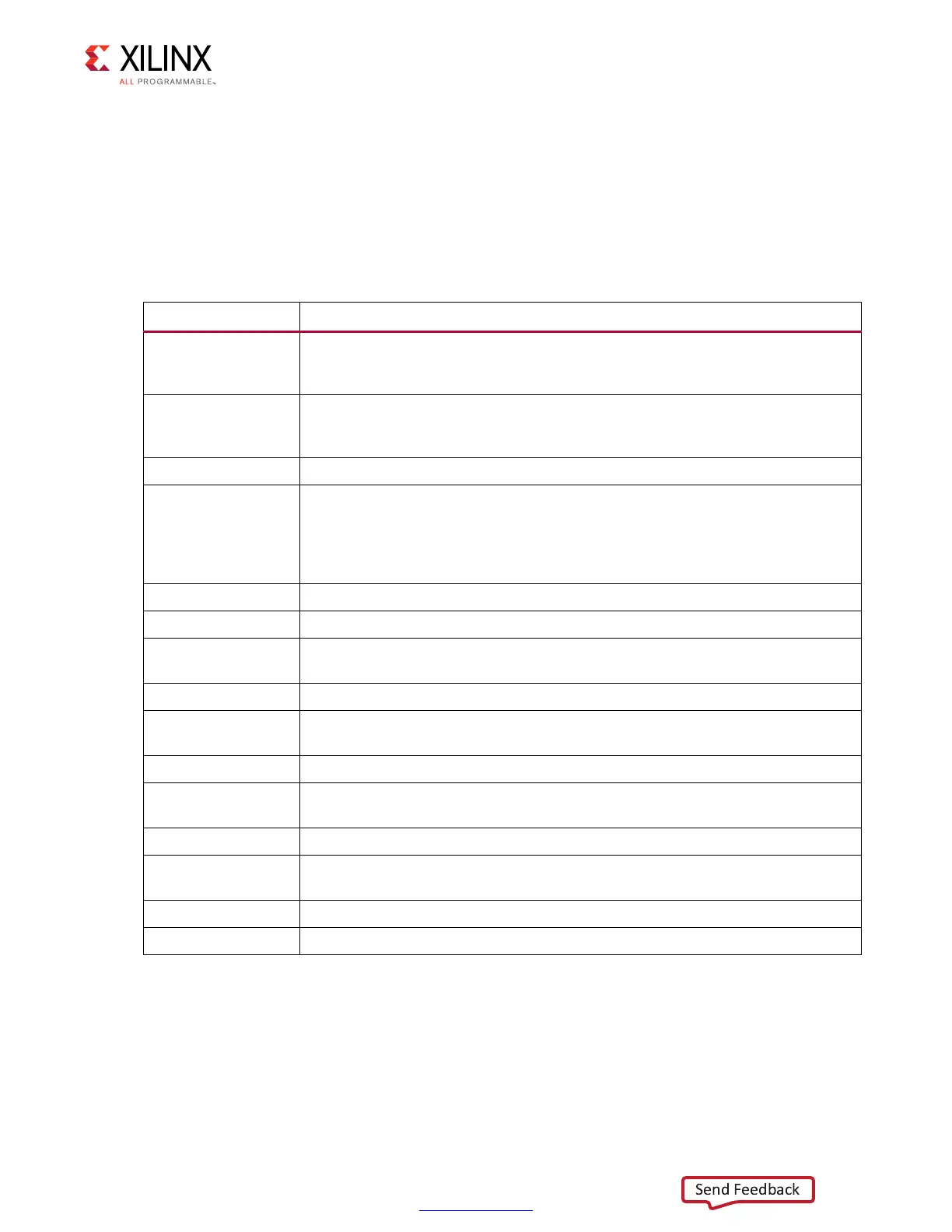

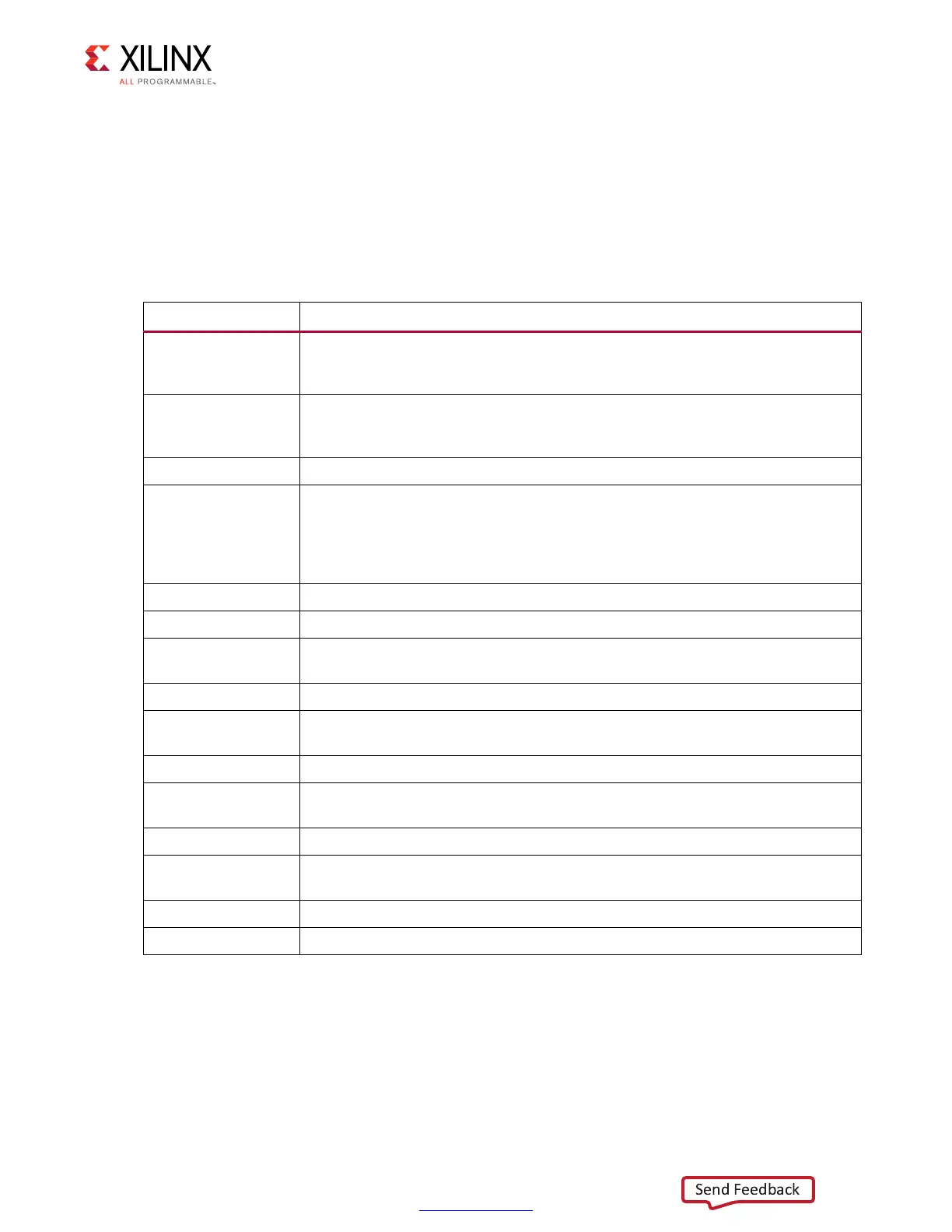

Table 3-26 shows the signals and parameters of interest, respectively, during simulation.

Table 3-26: Signals of Interest During Simulation

Signal Name Usage Signal Name Usage

tg_compare_error

This signal indicates a mismatch between the data written from the UI and data

received during a read on the UI. This signal is a part of the example design. A

single error asserts this signal; it is held until the design is reset.

dbg_cmp_err

This signal indicates a mismatch between the data written from the UI and the

data received during a read on the UI. This signal is part of the example design.

This signal is asserted each time a data mismatch occurs.

user_cmd_en This signal indicates if a command is valid.

user_cmd

This signal indicates if you requests a write or a read command.

2’b00 = Write Command

2’b01 = Read Command

2’b10 = NOP

2’b11 = NOP

user_addr This is the address location for the current command.

user_ba This is the bank address location for the current command.

user_wr_en

This signal is asserted when the user_wr_data is valid. This signal is necessary for

write commands.

user_wr_data This signal is the write data provided for write commands.

user_wr_dm

This signal is the data mask for masking off and not writing all of the data in a

given write transaction.

user_afifo_empty This signal indicates that the command and address FIFO is empty.

user_afifo_full

This signal indicates that the command and address FIFO is full. When this signal

is asserted additional commands and data is not accepted.

user_wdfifo_empty This signal indicates that the write data FIFO is empty.

user_wdfifo_full

This signal indicates that the write data FIFO is full. When this signal is asserted,

additional Write data is not accepted.

user_rd_valid Asserted when user_rd_data is valid.

user_rd_data Read data returned from the memory as a result of a read command.

Loading...

Loading...