Reference Manual ADuCM356

UART SERIAL INTERFACE

analog.com Rev. A | 255 of 312

UART and Power-Down Modes

Complete ongoing UART transfers before powering down the chip

into hibernate mode. Alternatively, disable the UART by clearing the

COMDIV register to 0x0000 before placing the device into hiberna-

tion. If hibernate mode is selected while a UART transfer is on,

the transfer does not continue on a return from hibernation. All the

intermediate data, states, and status logic in the UART are cleared.

However, the transmit pad (UART_SOUT) remains active in the

hibernate mode while transmitting. After hibernation, the UART can

be enabled by setting the COMDIV register, if previously cleared. If

DMA mode is needed, COMIEN, Bits[5:4] must be configured.

Table 319 details registers retained through hibernate mode. All

other registers and internal logic are cleared by a hardware default

value.

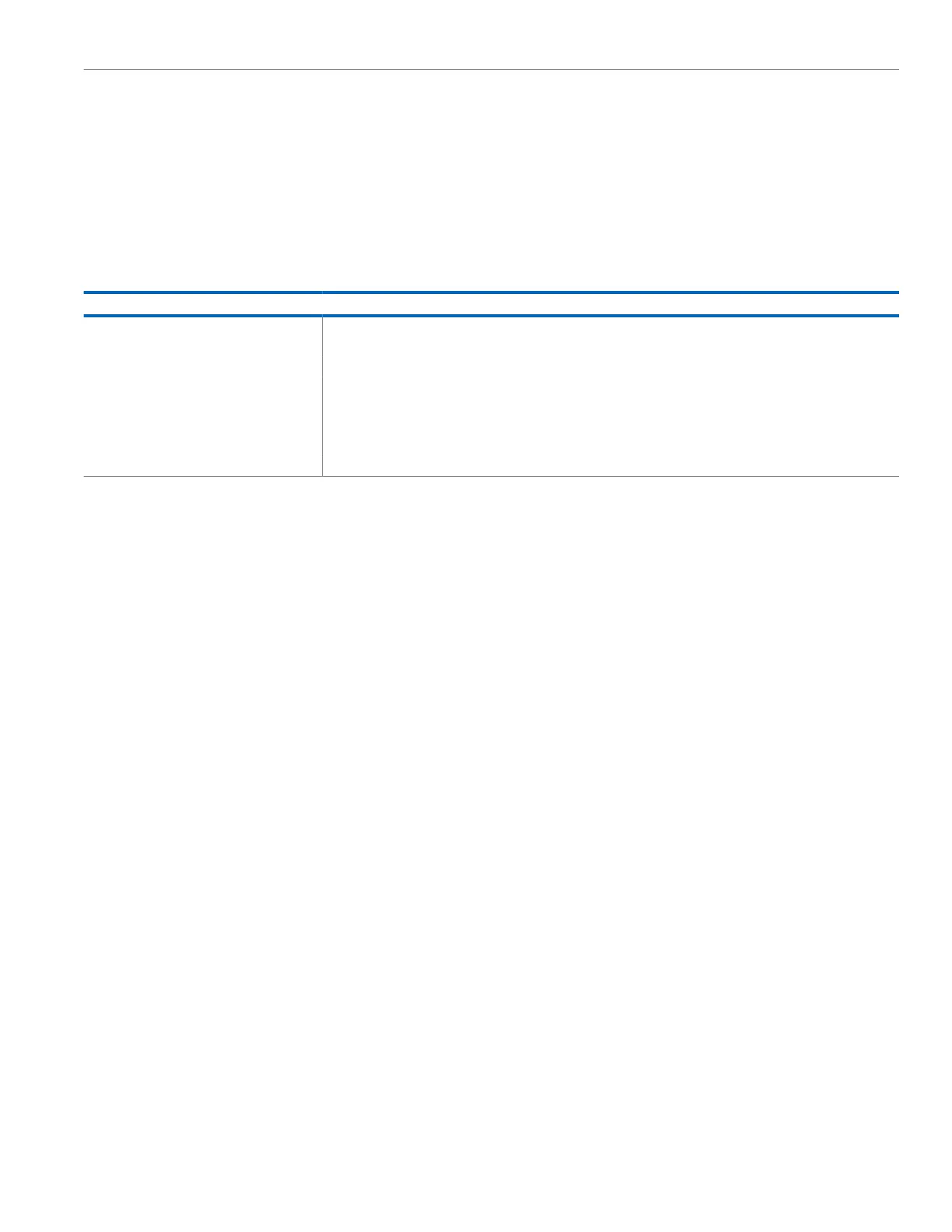

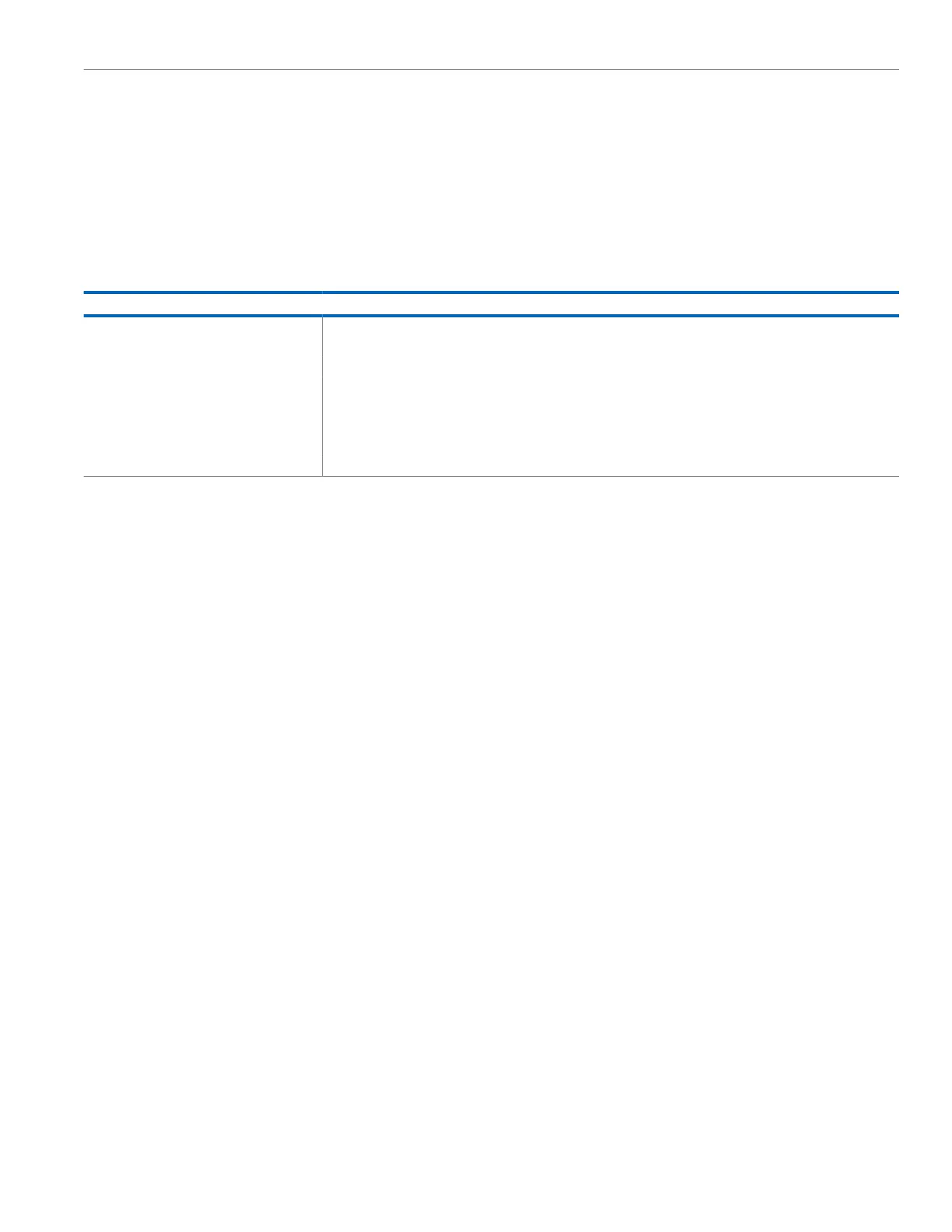

Table 319. Registers Retained Through Hibernate Mode

Register Affected Bits

COMIEN ELSI, ERBFI

COMLCR BRK, SP, EPS, PEN, WLS

COMFCR RFTRIG, FDMAMD, FIFOEN

COMFBR FBEN, DIVM, DIVN

COMDIV DIV

COMLCR2 OSR

COMCTL RXINV, FORCECLKON

COMRSC DISTX, DISRX, OENSP, OENP

Recommendations for UART Receive Wake-Up

from Hibernate Mode

If the UART receive input is used to wake the ADuCM356 from

hibernate mode, keep in mind that the UART block, along with

the rest of the ADuCM356 chip, requires 10 μs settling time after

the first falling edge of the UART wake-up byte. This delay means

that the first UART receive byte may not be read correctly by the

ADuCM356, especially with UART baud rates ≥ 57,600.

For reliable exit of hibernate mode via the UART receive pin,

perform one of the two following actions:

► Ensure that the wake-up character received by the ADuCM356 is

a break byte. On receiving a break byte, the ADuCM356 UART

sets the break indicator status flag in the COMLSR, Bit 4 register.

This flag generates an interrupt.

► Pull the ADuCM356 low for a period ≤1 μs. This setting triggers

the UART wake-up. After ≥10 μs, normal UART communications

can proceed.

Loading...

Loading...