Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 262

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

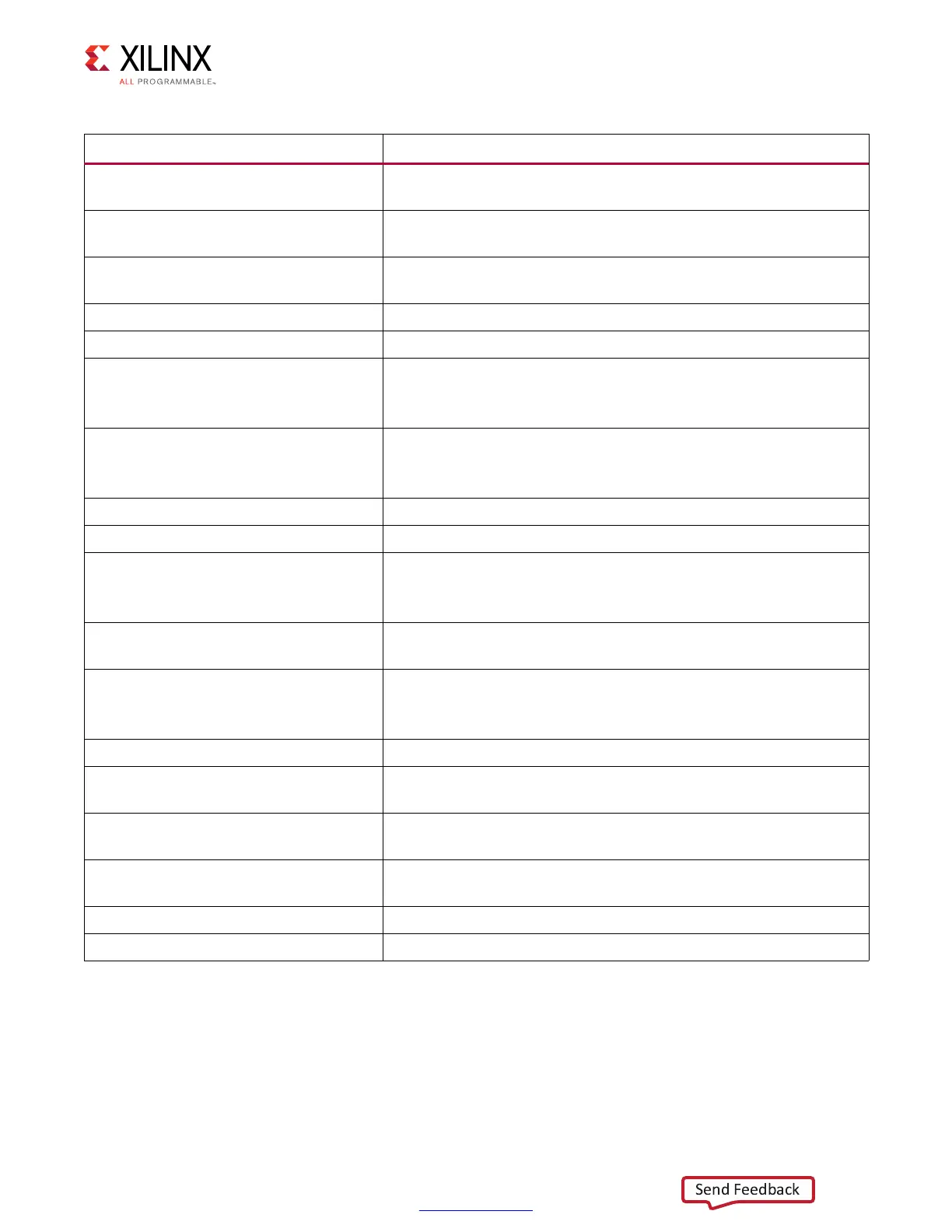

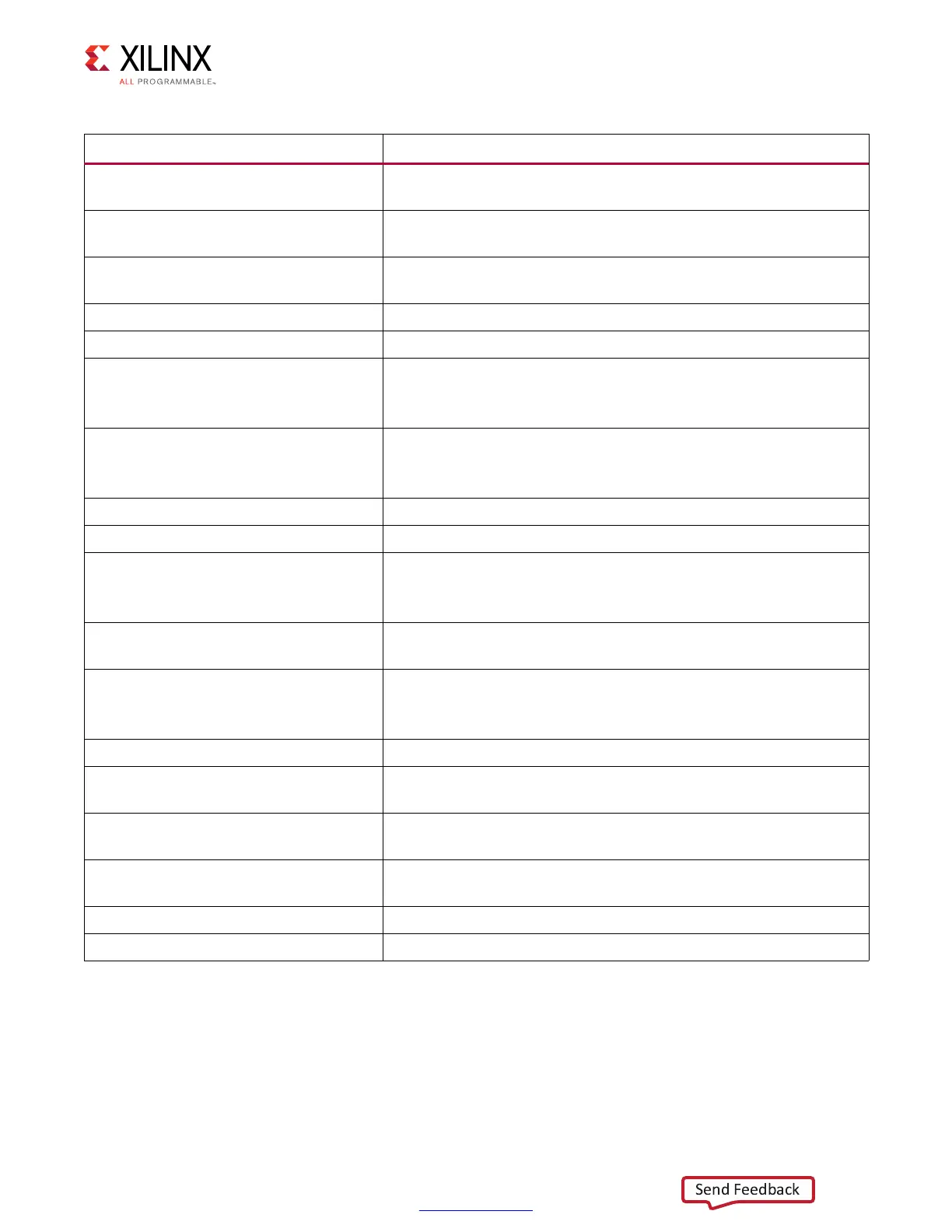

ref_bit

Signifies that reference bit of the byte which has largest left edge

PHASER_IN tap value.

complex_victim_inc Indicates the victim increment for internal calibration pattern change.

rd_victim_sel

Signifies the victim selection to get the correct data pattern to

compare during read back.

prbs_state_r1 Signifies the state of PRBS Read Leveling state machine.

rd_valid_r2 Indicates the read out data is valid to use for comparison.

left_edge_found_pb

Indicates left edge found for each bit in a byte.

Left_edge_found_pb[0] is for Bit[0] and left_edge_found_pb[7] is for

Bit[7].

right_edge_found_pb

Indicates right edge found for each bit in a byte.

right_edge_found_pb[0] is for Bit[0] and right_edge_found_pb[7] is

for Bit[7].

largest_left_edge Signifies the left edge tap value of the byte.

smallest_right_edge Signifies the right edge tap value of the byte.

fine_delay_incdec_pb

Indicates the increment of FINEDELAY tap in IDELAY primitive for

each bit in a byte. fine_delay_incdec_pb[0] is for Bit[0] and

fine_delay_incdec_pb[7] is for Bit[7].

fine_delay_sel

Indicates fine_delay_incdec_pb is applied for FINEDELAY in IDELAY

primitive.

compare_err_pb_latch_r

Indicates that data mismatch happened for each bit in a byte at a

specific PHASER_IN tap setting. compare_err_pb_latch_r[0] is for

Bit[0] and compare_err_pb_latch_r[7] is for Bit[7].

fine_pi_dec_cnt Signifies the computed decrease value of PHASER_IN tap.

match_flag_and

Indicates all bits have data mismatch. Recoded for five consecutive

PHASER_IN tap setting.

stage_cnt

Signifies the number of scans with different setting of FINEDELAY in

IDELAY primitive.

fine_inc_stage

Indicates that FINEDELAY in IDELAY primitive is in the increment

stage.

compare_err_pb_and Signifies the data mismatch happened for all bits in a byte.

right_edge_found Indicates the right edge of the byte is found.

Table 1-81: Debug Signals of Interest for PRBS Read Leveling Calibration (Cont’d)

Debug Signal Signal Description

Loading...

Loading...