Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 264

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

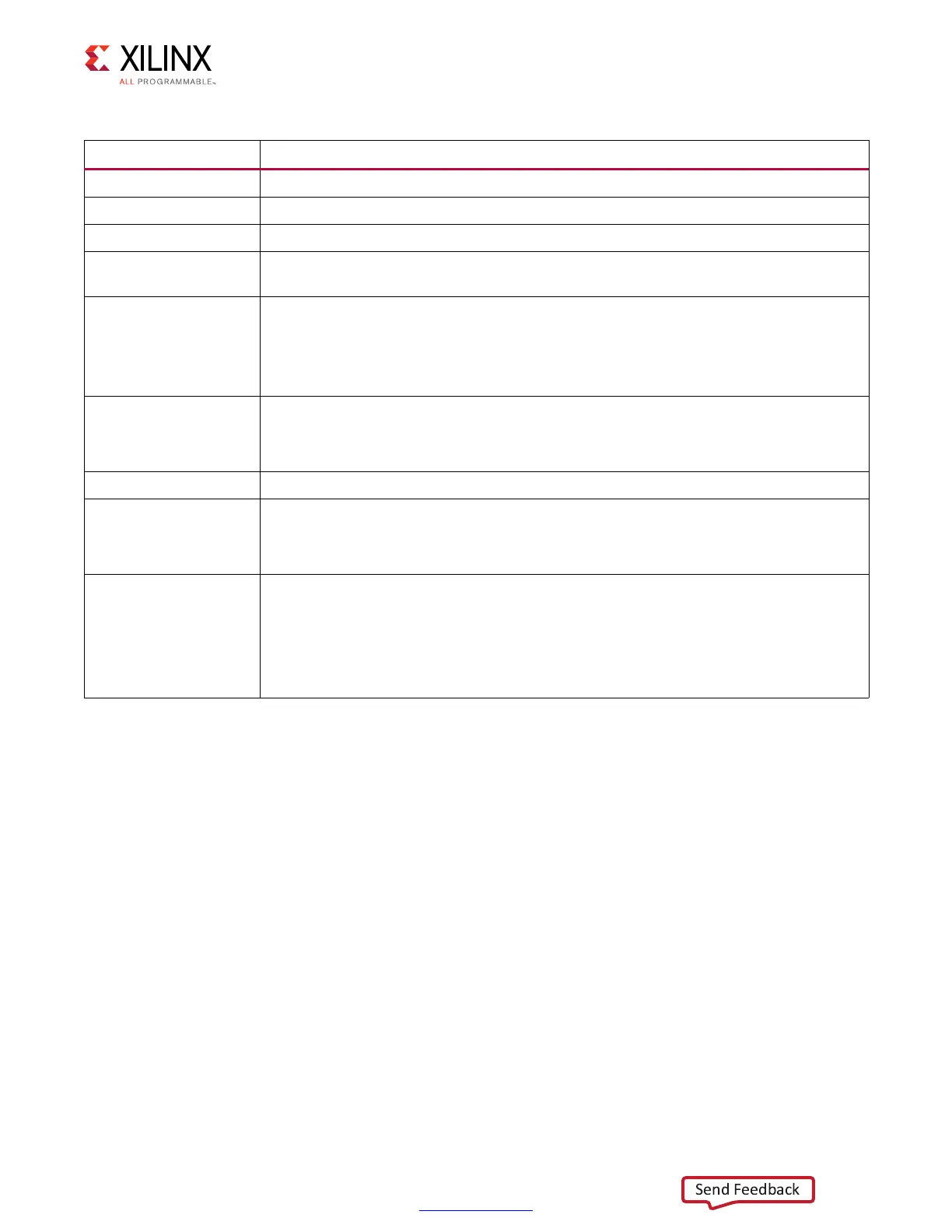

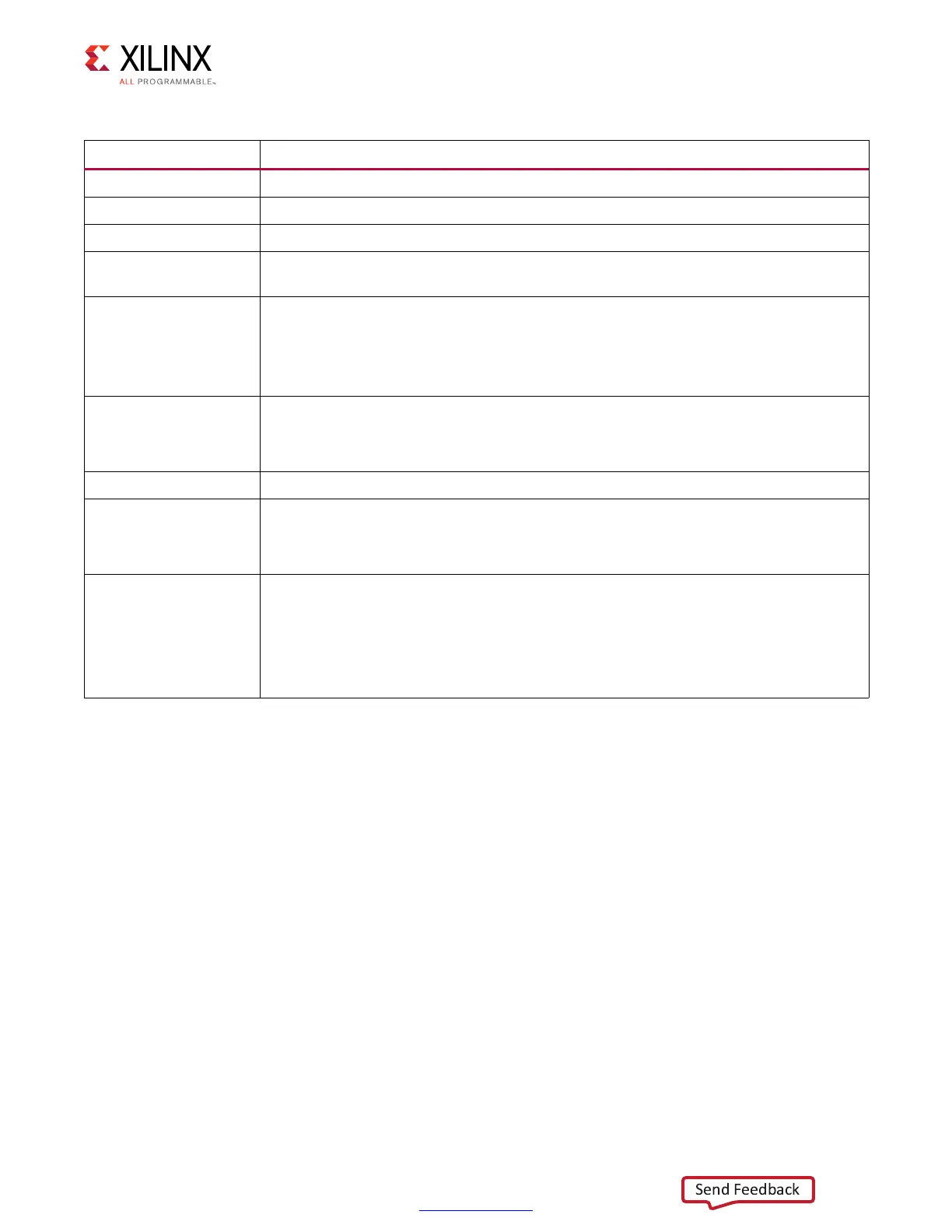

Table 1-83: Debug Signals Used for Configuring the Traffic Generator

Signal Name Description

vio_modify_enable Set to 1 to vary the command Traffic Generator command pattern.

vio_data_mask_gen Traffic generator Data Mask generation.

vio_pause_traffic Set to 1 to pause the Traffic Generator.

dbg_clear_error

Set to clear Traffic Generator errors. This signal can be used in checking for single bit

errors or measuring a read window.

vio_addr_mode_value

Valid settings for this signal are:

• 0x1 = FIXED address mode

(1)

• 0x2 = PRBS address mode

• 0x3 = SEQUENTIAL address mode

vio_bl_mode_value

Valid settings for this signal are:

• 0x1 = FIXED burst length

(1)

•0x2 = PRBS burst length

vio_fixed_bl_value Valid settings are 1 to 256.

vio_fixed_instr_value

Valid settings are:

• 0x0 = Write instruction

• 0x1 = Read instruction

vio_instr_mode_value

Valid settings for this signal are:

• 0x1 = Command type (read/write) as defined by fixed_instr_i

(1)

• 0x2 = Random read/write commands

• 0xE = Write only at address zero

• 0xF = Read only at address zero

Loading...

Loading...