Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 306

UG586 November 30, 2016

www.xilinx.com

Chapter 2: QDR II+ Memory Interface Solution

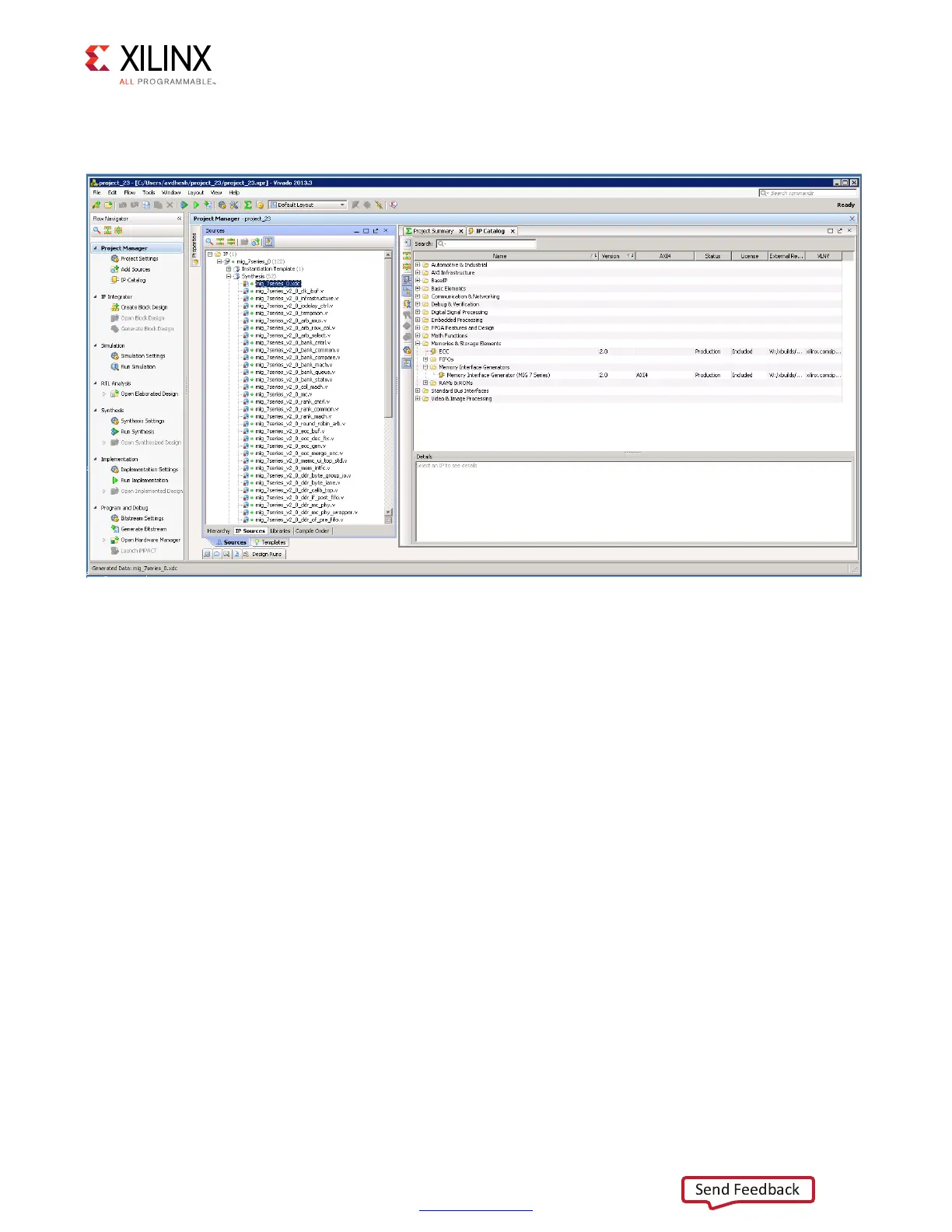

8. All user-design RTL and constraints files (XDC files) can be viewed in the Sources >

Libraries tab (Figure 2-34).

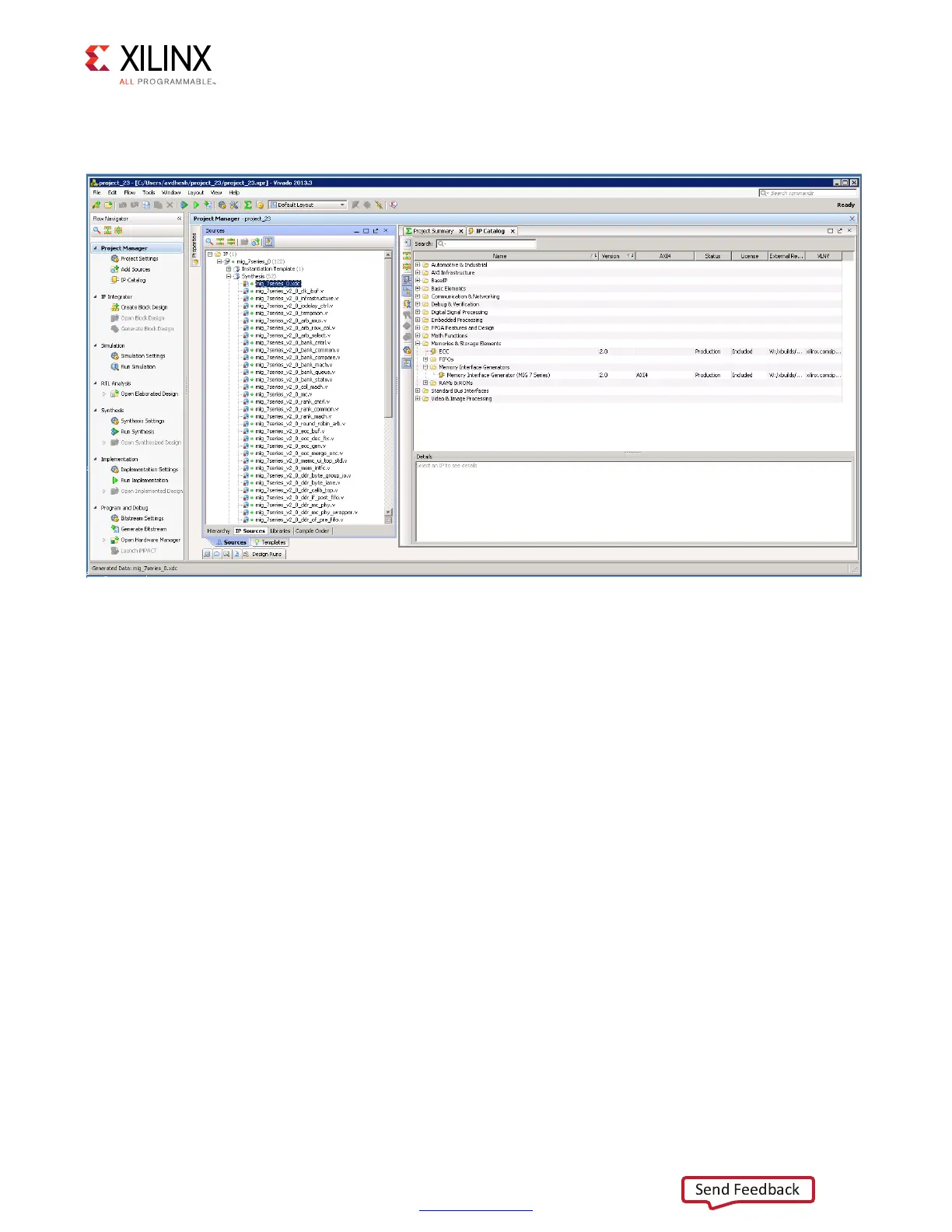

9. The Vivado Design Suite supports the Open IP Example Design flow. To create the

example design using this flow, right-click the IP in the Source Window, as shown in

Figure 2-35 and select.

X-Ref Target - Figure 2-34

Figure 2-34: Vivado Project – RTL and Constraints Files

Loading...

Loading...