Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 360

UG586 November 30, 2016

www.xilinx.com

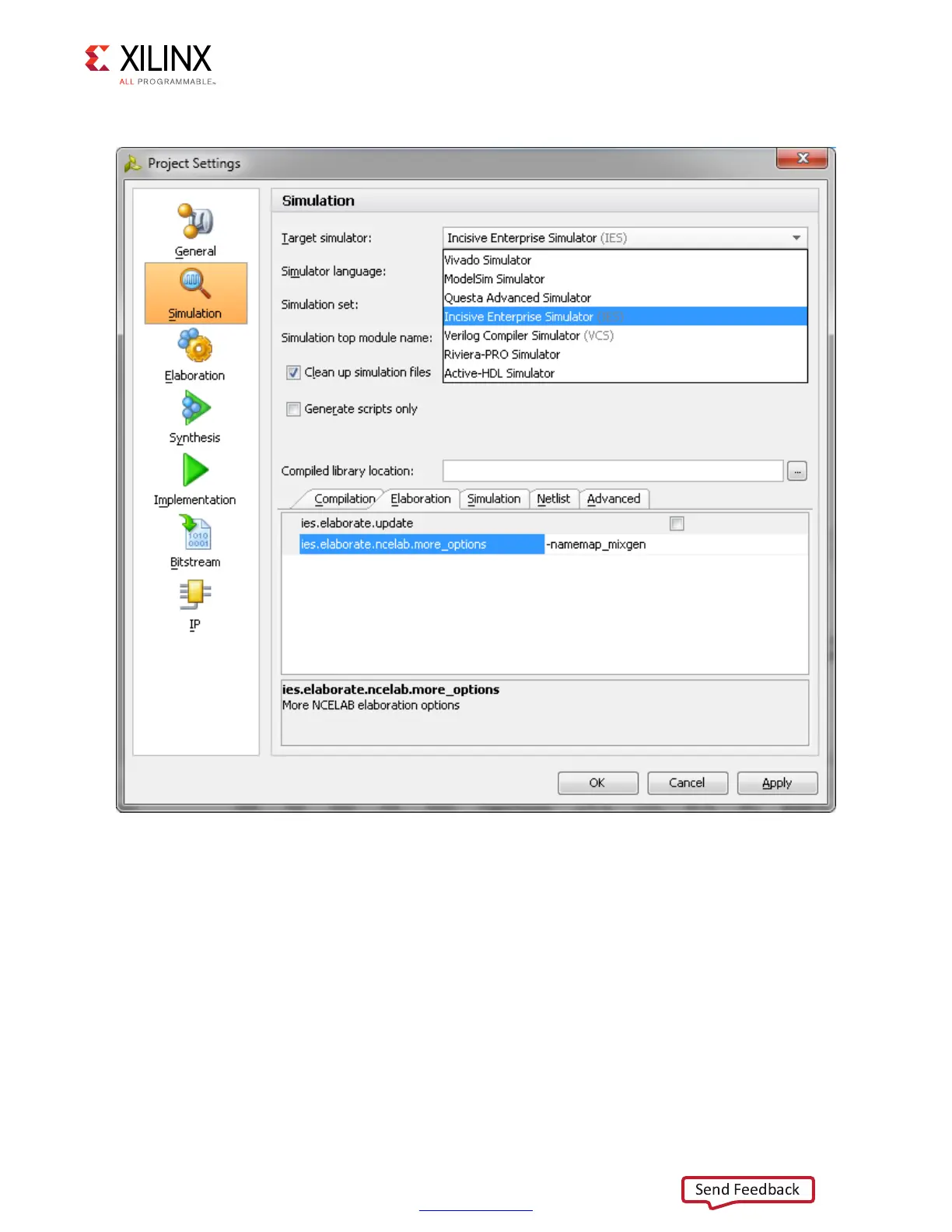

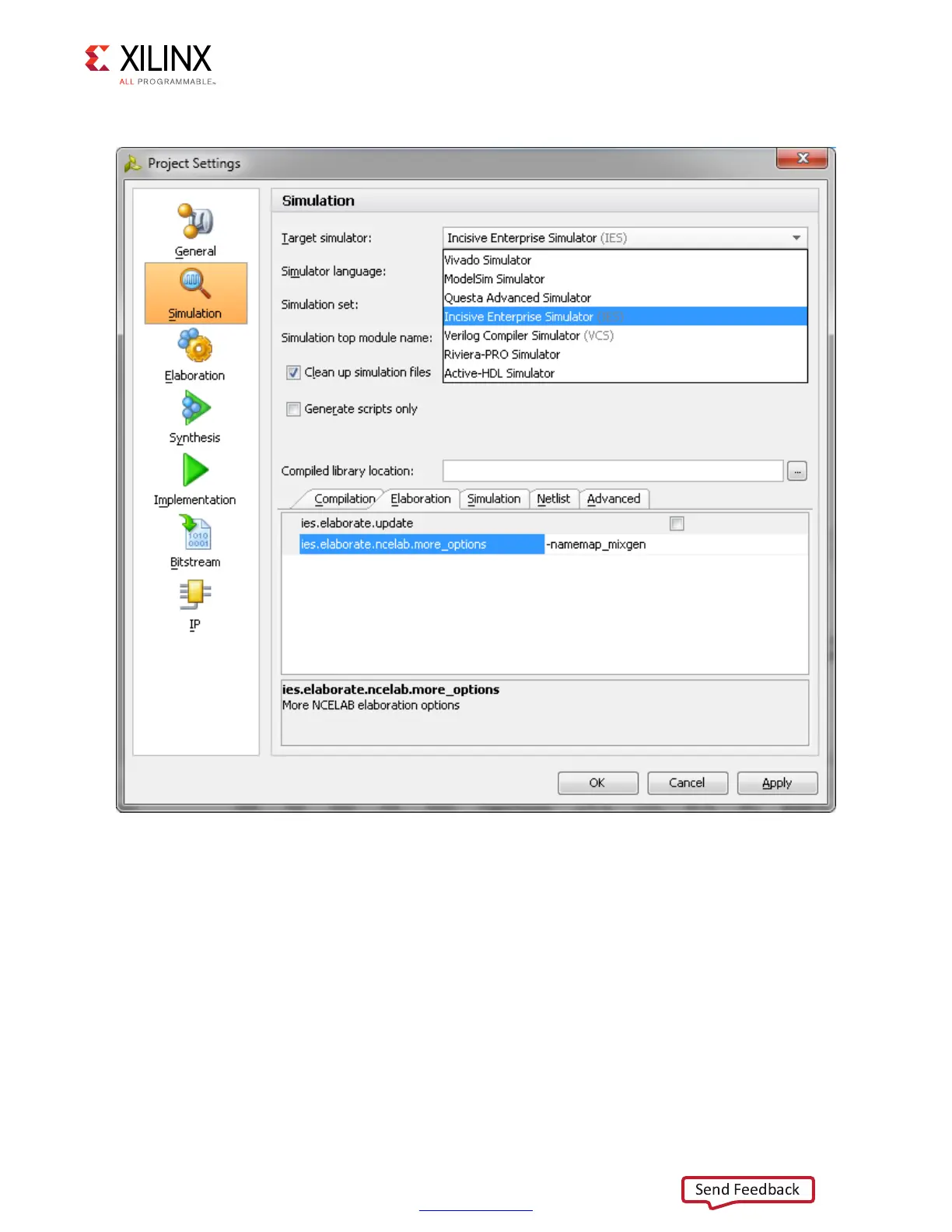

Chapter 2: QDR II+ Memory Interface Solution

3. Apply the settings and select OK.

4. In the Flow Navigator window, select Run Simulation and select Run Behavioral

Simulation as shown in Figure 2-51.

5. Vivado invokes IES and simulations are run in the IES tool. For more information, see the

Vivado Design Suite User Guide: Logic Simulation (UG900) [Ref 8].

Note:

MIG does not generate memory model files for QDR II+ designs. Appropriate memory model

should be added to the Simulation Sources under Sources window of the Open IP Example Design

project.

For Samsung Memory models appropriate define values should be added to the memory model

itself. Vivado settings does not allow applying define values explicitly on memory models.

X-Ref Target - Figure 2-54

Figure 2-54: Simulation with IES

Loading...

Loading...