Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 428

UG586 November 30, 2016

www.xilinx.com

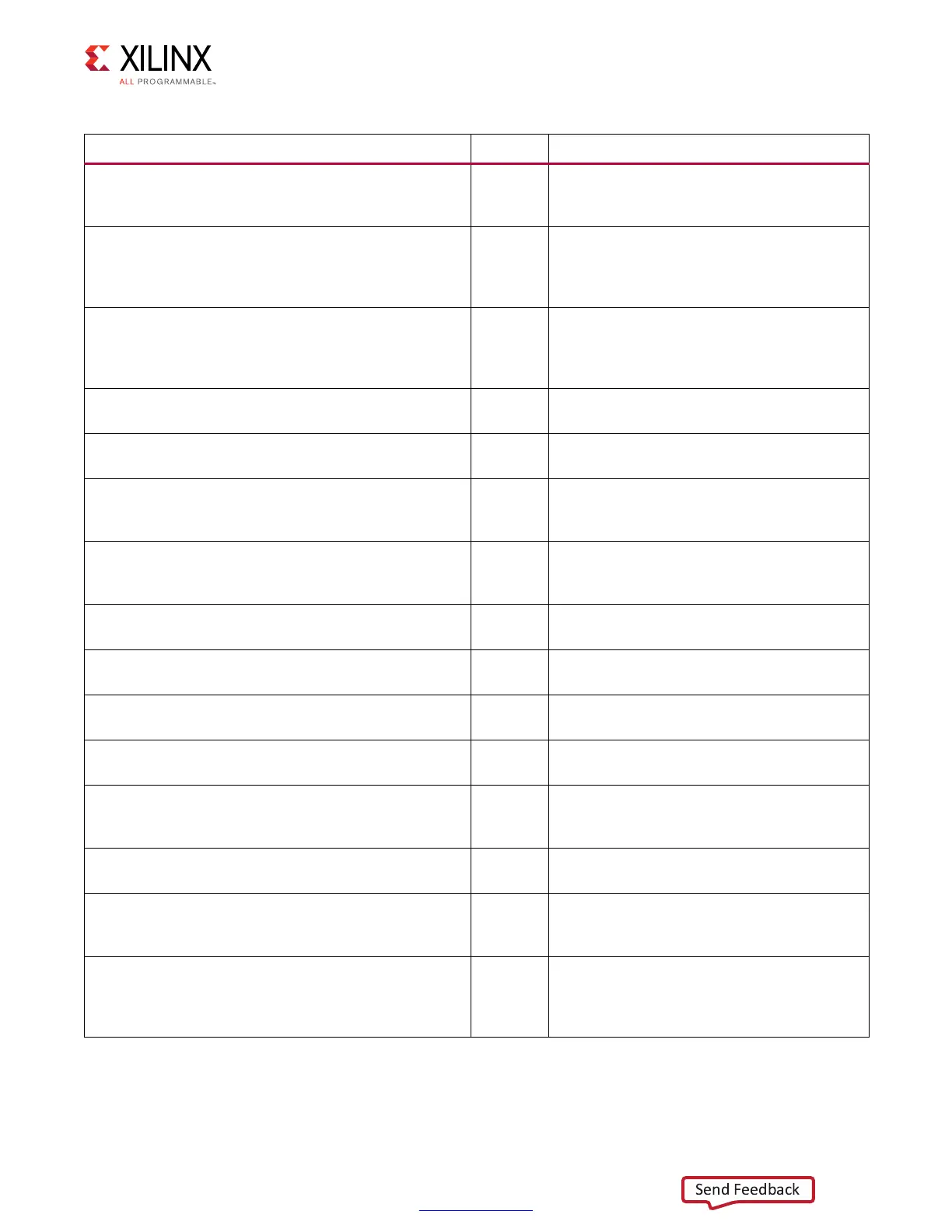

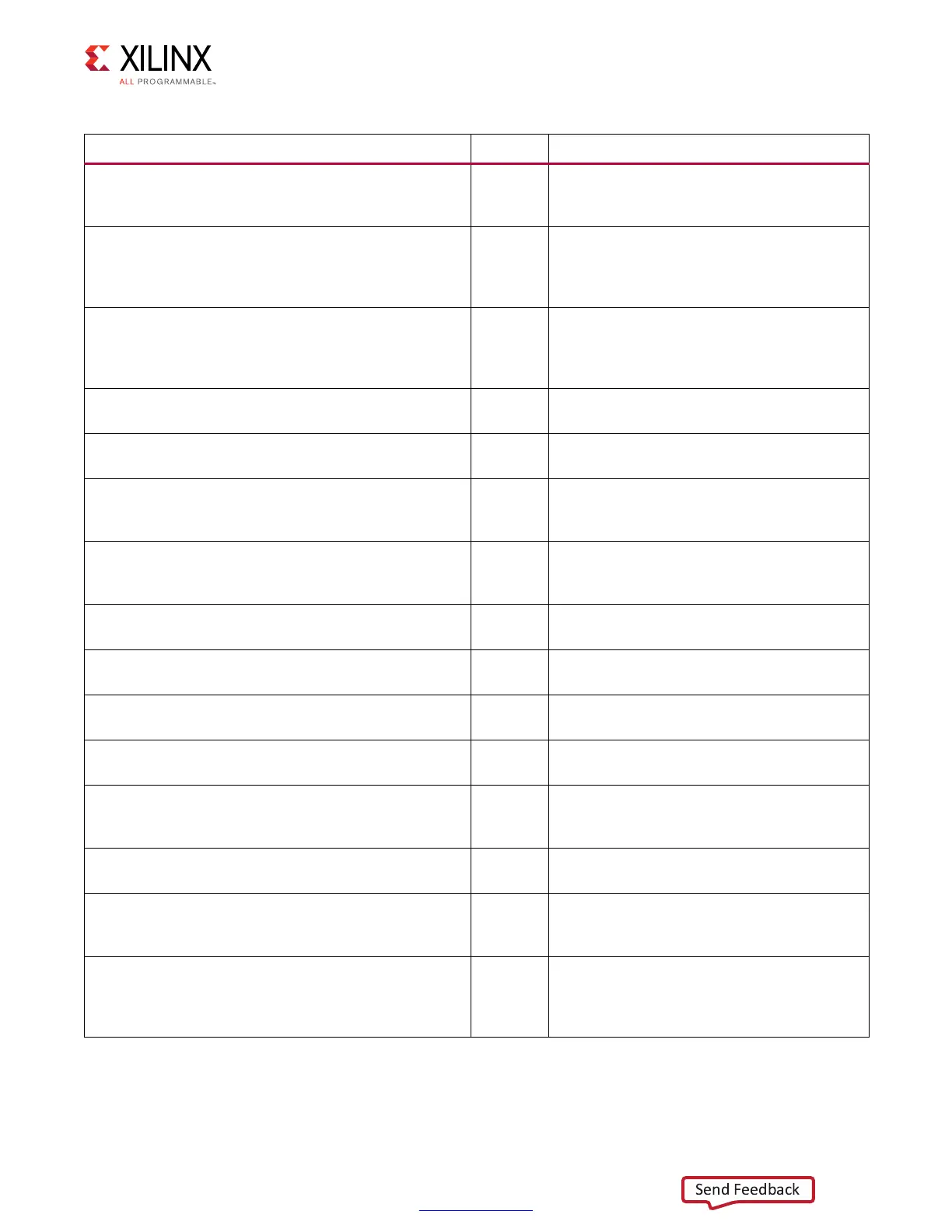

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

user_wr_en Input

Write Data Enable. This signal issues the write

data and data mask. It indicates that the

corresponding user_wr_* signals are valid.

user_wr_data[2 × nCK_PER_CLK × DATA_WIDTH – 1:0] Input

Write Data. This is the data to use for a write

request and is composed of the rise and fall

data concatenated together. It is valid when

user_wr_en is asserted.

user_wr_dm[2 × nCK_PER_CLK × DM_WIDTH – 1:0] Input

Write Data Mask. When active-High, the write

data for a given selected device is masked

and not written to the memory. It is valid

when user_wr_en is asserted.

user_afifo_empty Output

Address FIFO empty. If asserted, the

command buffer is empty.

user_wdfifo_empty Output

Write Data FIFO empty. If asserted, the write

data buffer is empty.

user_afifo_full Output

Address FIFO full. If asserted, the command

buffer is full, and any writes to the FIFO are

ignored until deasserted.

user_wdfifo_full Output

Write Data FIFO full. If asserted, the write

data buffer is full, and any writes to the FIFO

are ignored until deasserted.

user_afifo_aempty Output

Address FIFO almost empty. If asserted, the

command buffer is almost empty.

user_afifo_afull Output

Address FIFO almost full. If asserted, the

command buffer is almost full.

user_wdfifo_aempty Output

Write Data FIFO almost empty. If asserted,

the write data buffer is almost empty.

user_wdfifo_afull Output

Write Data FIFO almost full. If asserted, the

Write Data buffer is almost full.

user_rd_valid[nCK_PER_CLK – 1:0] Output

Read Valid. This signal indicates that data

read back from memory is available on

user_rd_data and should be sampled.

user_rd_data[2 × nCK_PER_CLK × DATA_WIDTH – 1:0] Output

Read Data. This is the data r ead b ack f rom t he

read command.

init_calib_complete Output

Calibration Done. This signal indicates back

to the user design that read calibration is

complete and requests can now take place.

mem_ck_lock_complete Output

Memory CK Lock Done. The system should be

kept in a quiet state until assertion of

mem_ck_lock_complete to ensure minimal

noise on the CK being driven to the memory.

Table 3-9: Client Interface Request Signals (Cont’d)

Signal Direction Description

Loading...

Loading...