Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 504

UG586 November 30, 2016

www.xilinx.com

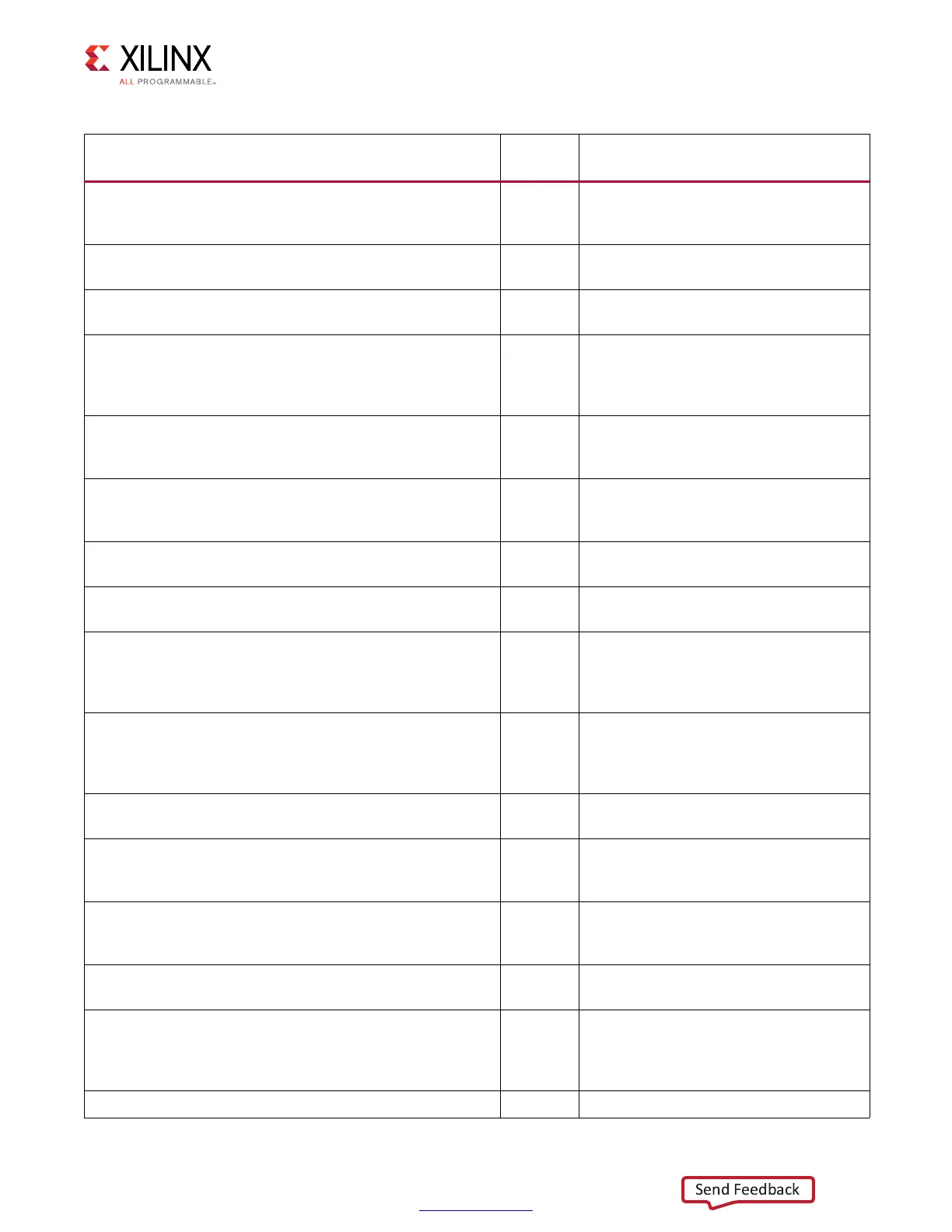

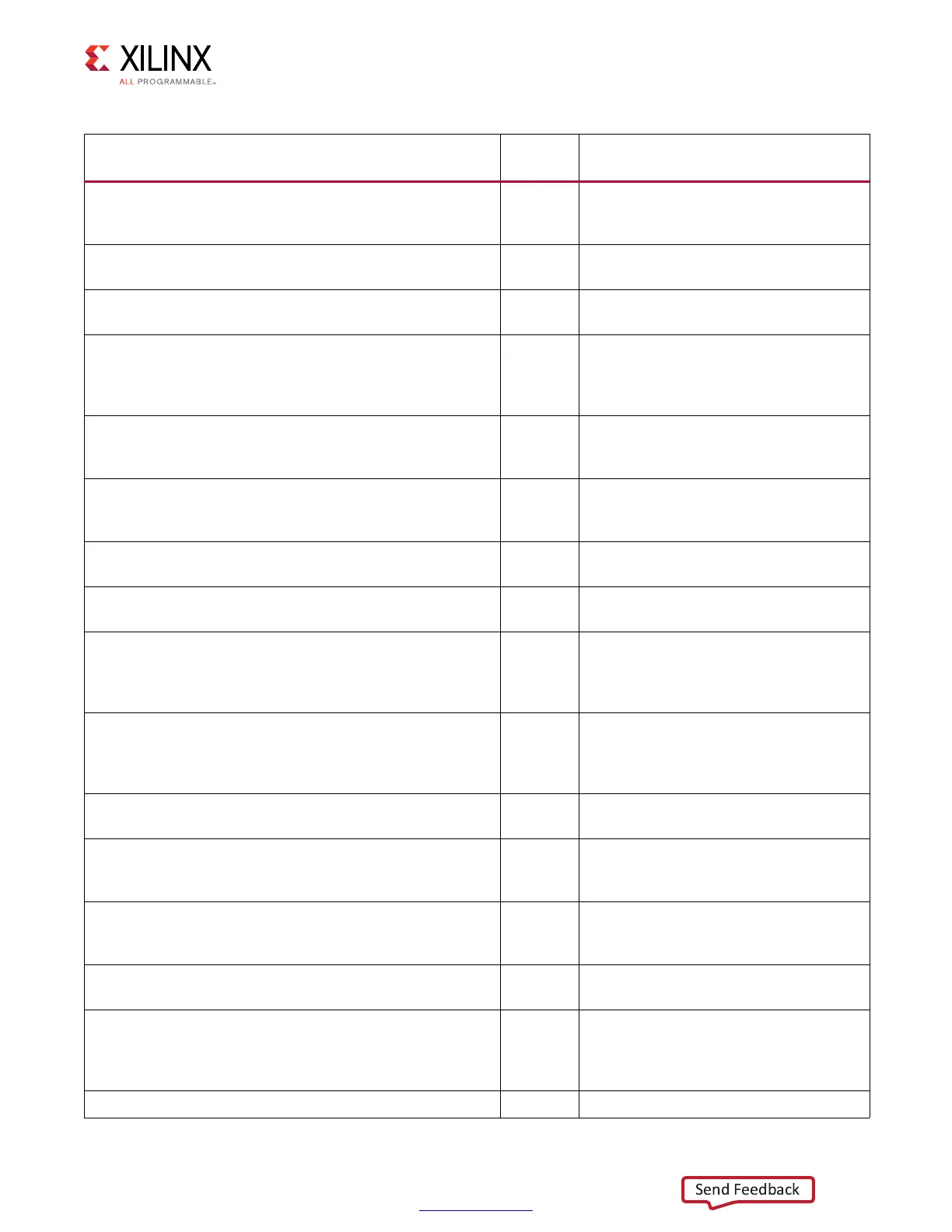

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

dbg_po_f_dec Input

This signal increments the PHASER_OUT

generated OSERDES clk that is used to

capture falling data.

dbg_pi_tap_cnt[5:0] Output

This output indicates the current

PHASER_IN tap count position.

dbg_po_tap_cnt[5:0] Output

This output indicates the current

PHASER_OUT tap count position.

dbg_rd_stage1_rtr_error[N_DATA_LANES – 1:0] Output

(RLDRAM 3 only) Per byte lane error

signal indicating valid window not found

during read training register stage 1 read

calibration.

dbg_rd_stage1_error[N_DATA_LANES – 1:0] Output

Per byte lane error signal indicating valid

window not found during stage 1 read

calibration.

dbg_cq_num[CQ_BITS – 1:0] Output

This signal indicates the current byte

lane selected (either during calibration

or through the debug port).

dbg_valid_lat[4:0] Output

Latency in cycles of the delayed read

command.

dbg_idel_tap_cnt_sel[TAP_BITS – 1:0] Output

Current IDELAY tap setting for bits

selected using dbg_bit_sel.

dbg_inc_latency Output

This output indicates that the latency of

the corresponding byte lane was

increased to ensure proper alignment of

the read data to the user interface.

dbg_error_max_latency Output

This signal indicates that the latency

could not be measured before the

counter overflowed. Each device has one

error bit.

dbg_error_adj_latency Output

This signal indicates that the target

PHY_LATENCY could not be achieved.

dbg_rd_data_rd[nCK_PER_CLK × 9 – 1:0] Output

This bus shows the captured output of

the rising data for a single byte lane,

selected using dbg_byte_sel.

dbg_rd_data_fd[nCK_PER_CLK × 9 – 1:0] Output

This bus shows the captured output of

the falling data for a single byte lane,

selected using dbg_byte_sel.

dbg_rd_valid Output

Read data valid signal that aligns with

the dbg_rd_data_rd and dbg_rd_data_fd.

dbg_wrcal_sel_stg[1:0] Input

Selects which stage of write calibration

to output: dbg_wrcal_po_first_edge,

dbg_wrcal_po_second_edge, or

dbg_wrcal_po_final.

dbg_wrcal[63:0] Output General Debug port for write calibration

Table 3-28: DEBUG_PORT Signal Descriptions (Cont’d)

Signal Direction Description

Loading...

Loading...