Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 661

UG586 November 30, 2016

www.xilinx.com

Chapter 5: Multicontroller Design

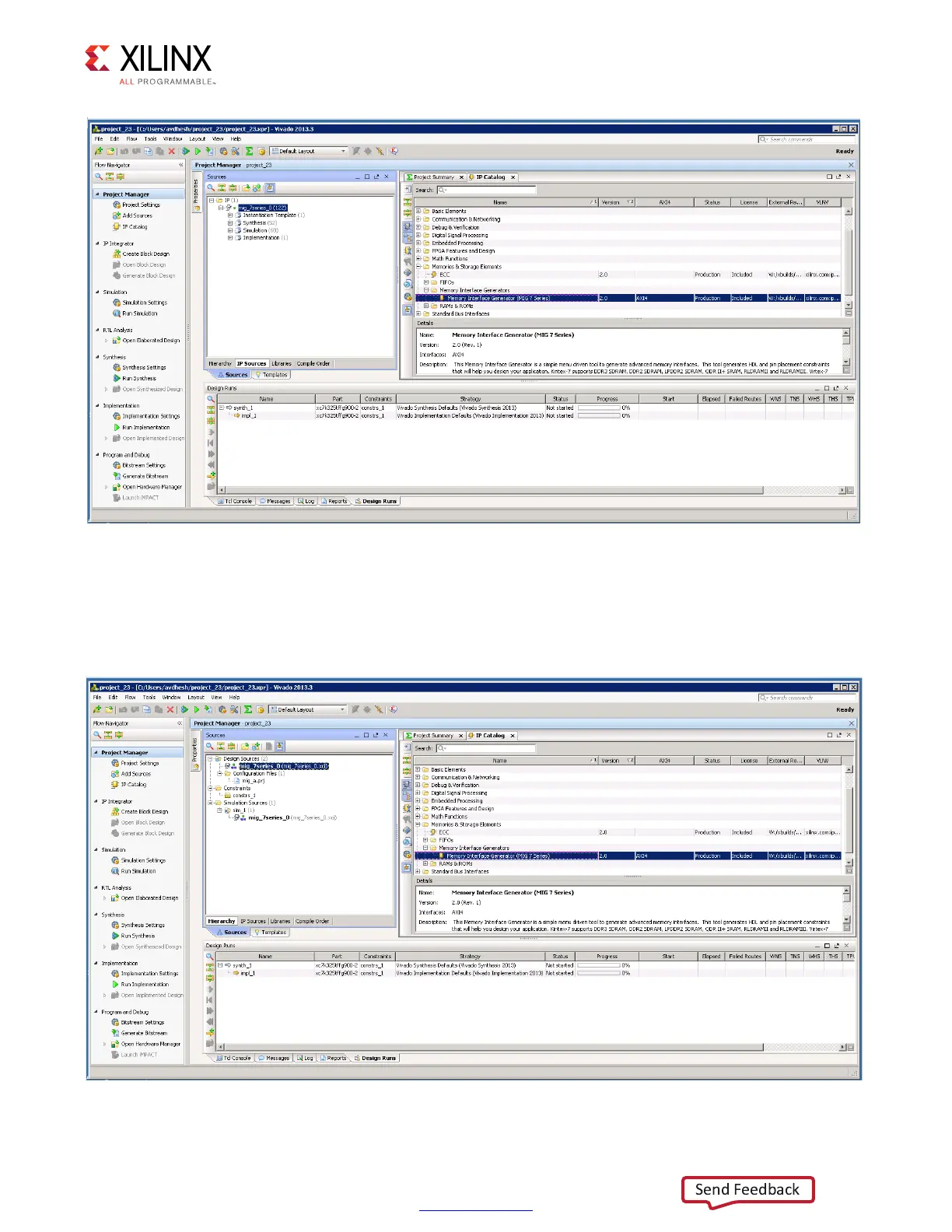

5. After project creation, the XCI file is added to the Project Hierarchy. The same view also

displays the module hierarchies of the user design. The list of HDL and XDC files is

available in the IP Sources view in the Sources window. Double-clicking on any module

or file opens the file in the Vivado Editor. These files are read only.

X-Ref Target - Figure 5-21

Figure 5-21: Vivado Tool Project Window (After IP Generation)

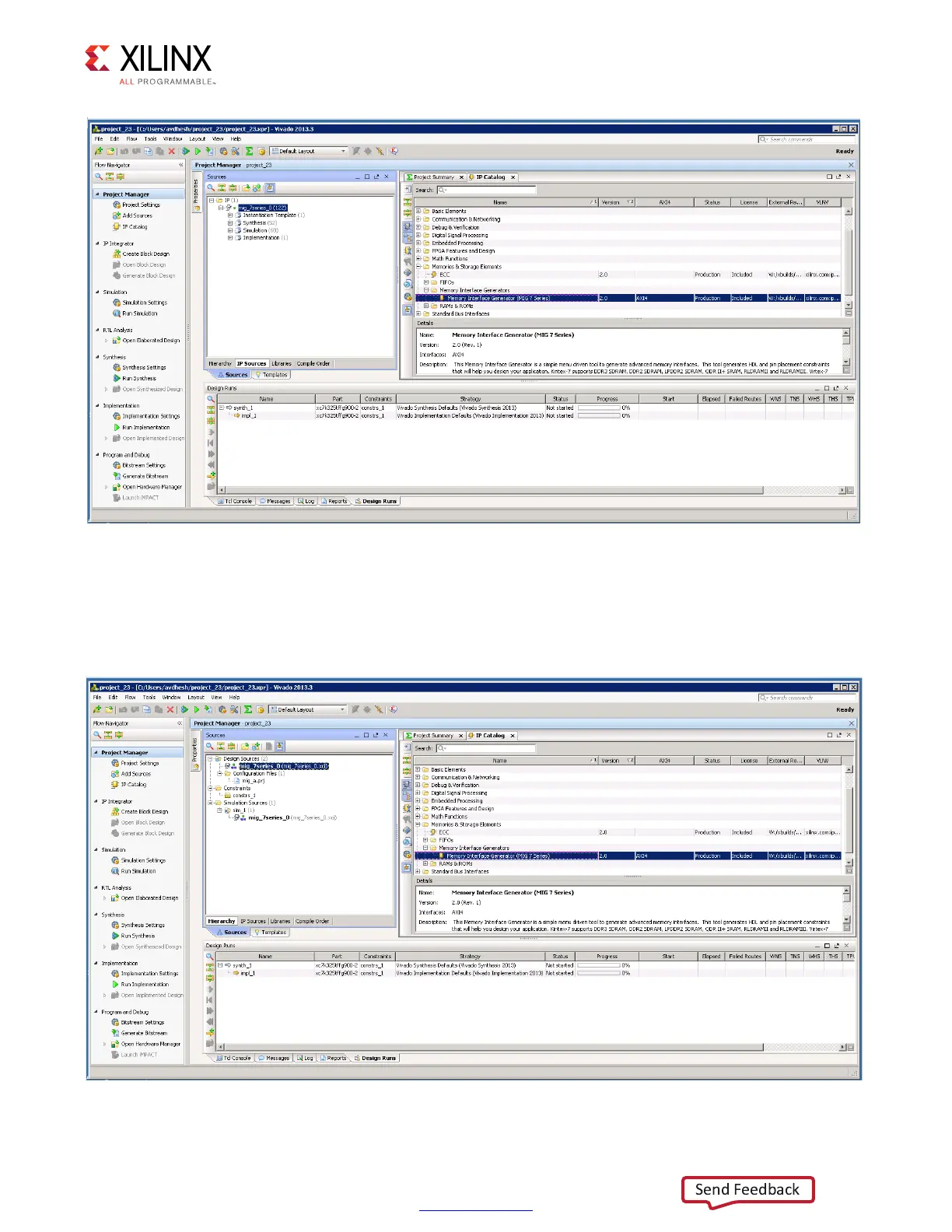

X-Ref Target - Figure 5-22

Figure 5-22: Vivado Tool Project Sources Window

Loading...

Loading...