Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 662

UG586 November 30, 2016

www.xilinx.com

Chapter 5: Multicontroller Design

Design generation from MIG can be generated using the Create Design flow or the

Verify Pin Changes and Update Design flow. There is no difference between the flow

when generating the design from the MIG tool. Irrespective of the flow by which designs

are generated from the MIG tool, the XCI file is added to the Vivado project. The

implementation flow is the same for all scenarios because the flow depends on the XCI

file added to the project.

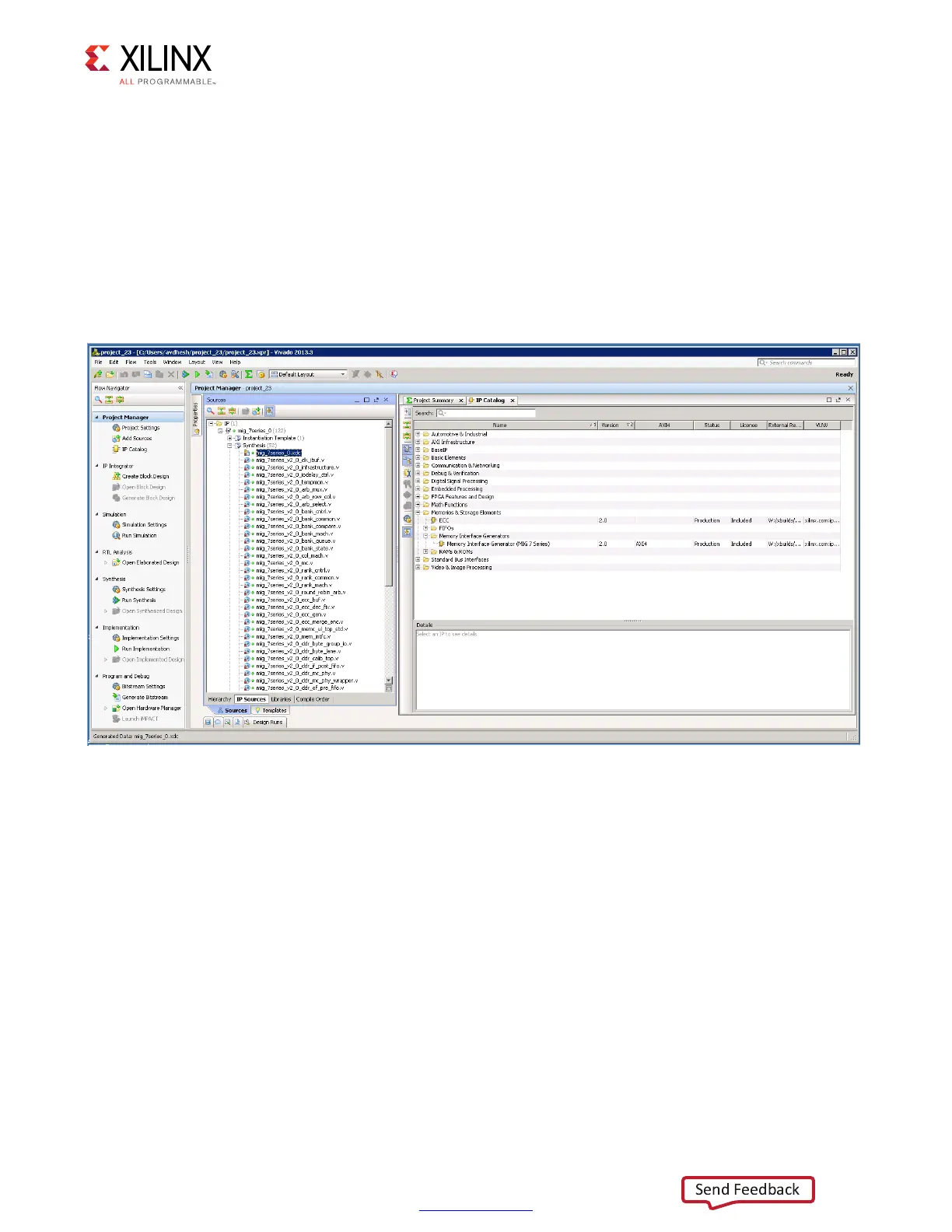

6. All MIG generated user design RTL and XDC files are automatically added to the project.

If files are modified and you wish to regenerate them, right-click the XCI file and select

Generate Output Products (Figure 5-23).

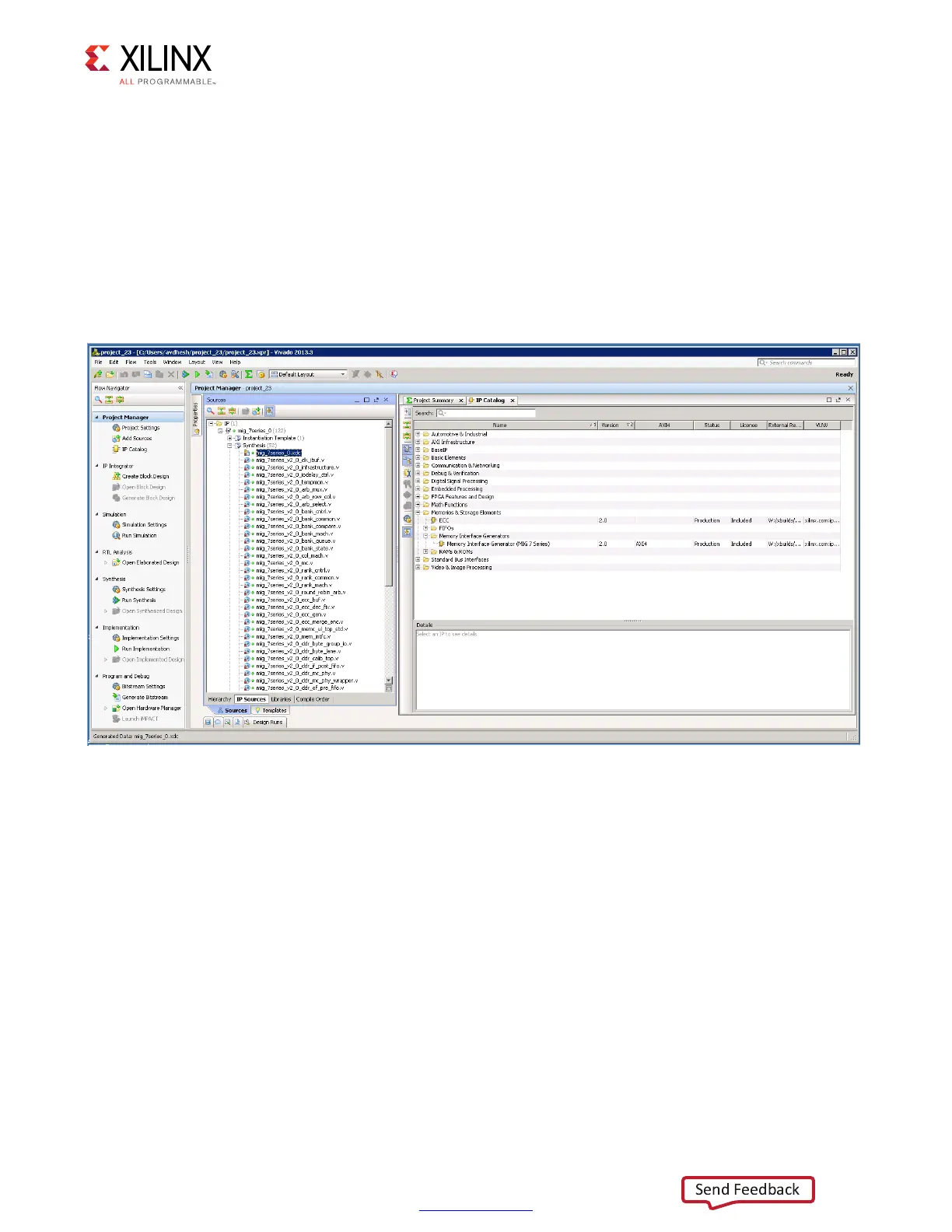

7. Clicking Generate Output Products option brings up the Manage Outputs window

(Figure 5-24).

X-Ref Target - Figure 5-23

Figure 5-23: Generate RTL and Constraints

Loading...

Loading...