Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 664

UG586 November 30, 2016

www.xilinx.com

Chapter 5: Multicontroller Design

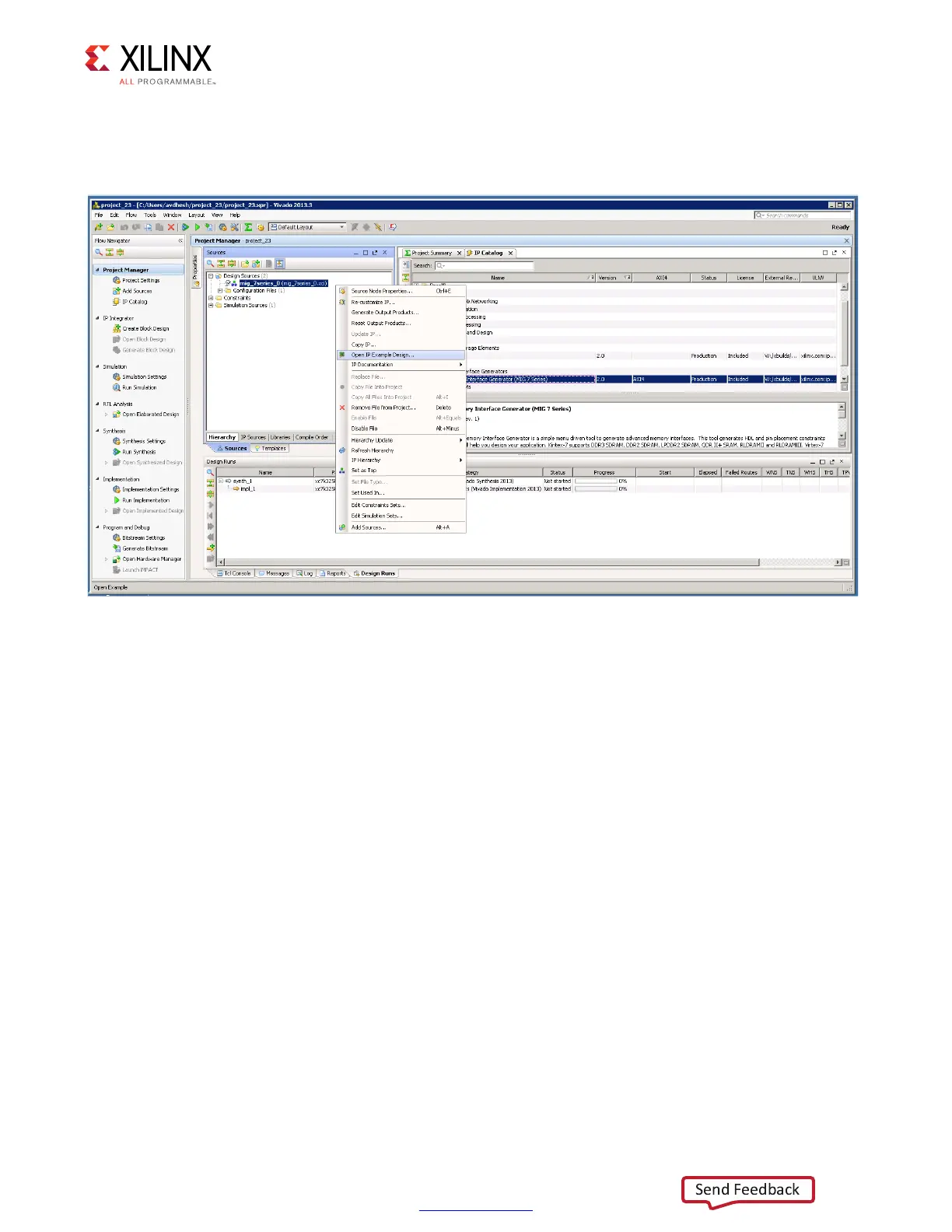

9. The Vivado Design Suite supports Open IP Example Design flow. To create the example

design using this flow right-click the IP in the Source Window, as shown in Figure 5-26

and select.

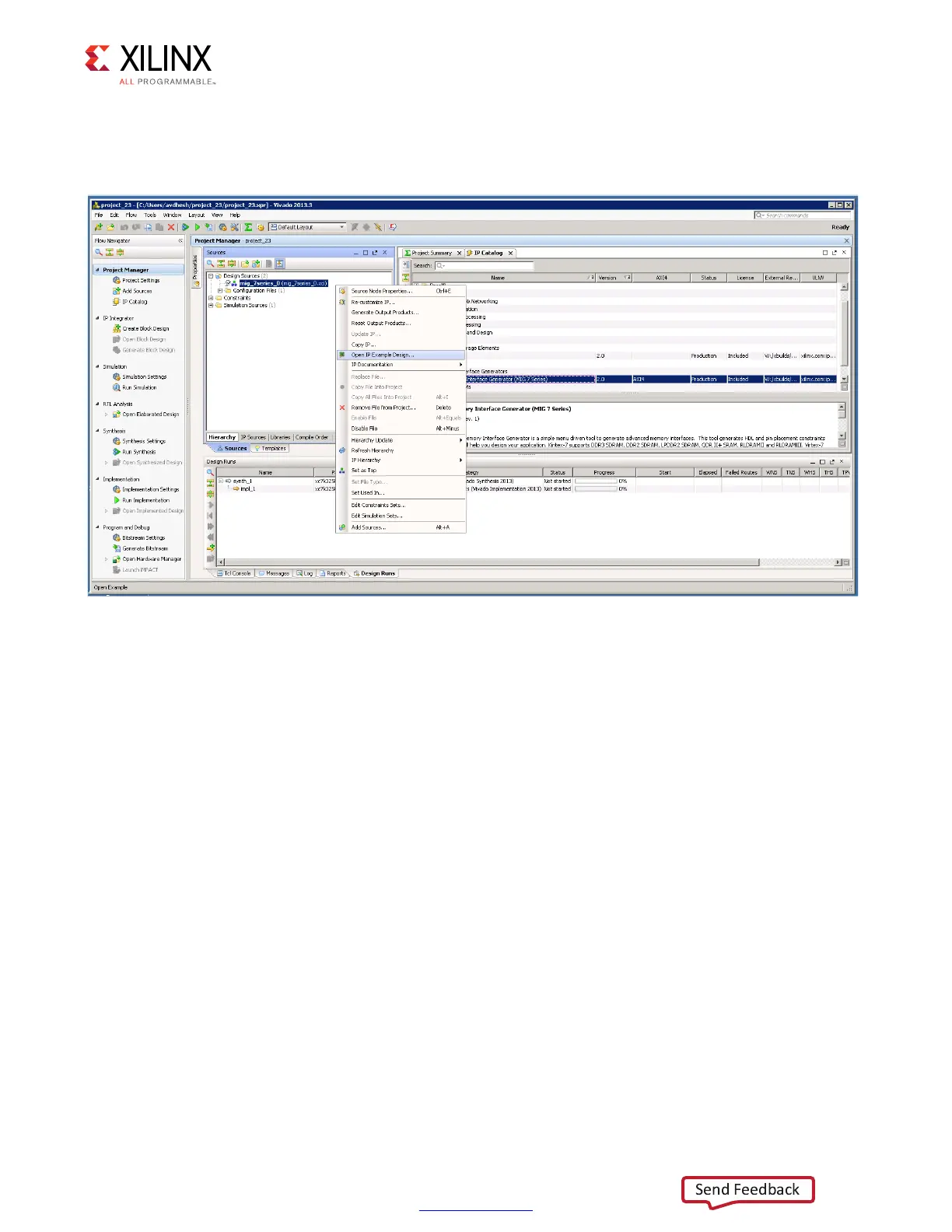

10. This option creates a new Vivado project. Selecting the menu brings up a dialog box,

which guides you to the directory for a new design project. Select a directory (or use the

defaults) and click OK.

This launches a new Vivado project with all example design files and a copy of the IP.

This project has example_top as the Implementation top directory, and sim_tb_top

as the Simulation top directory, as shown in Figure 5-27.

X-Ref Target - Figure 5-26

Figure 5-26: Open IP Example Design

Loading...

Loading...