Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 79

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

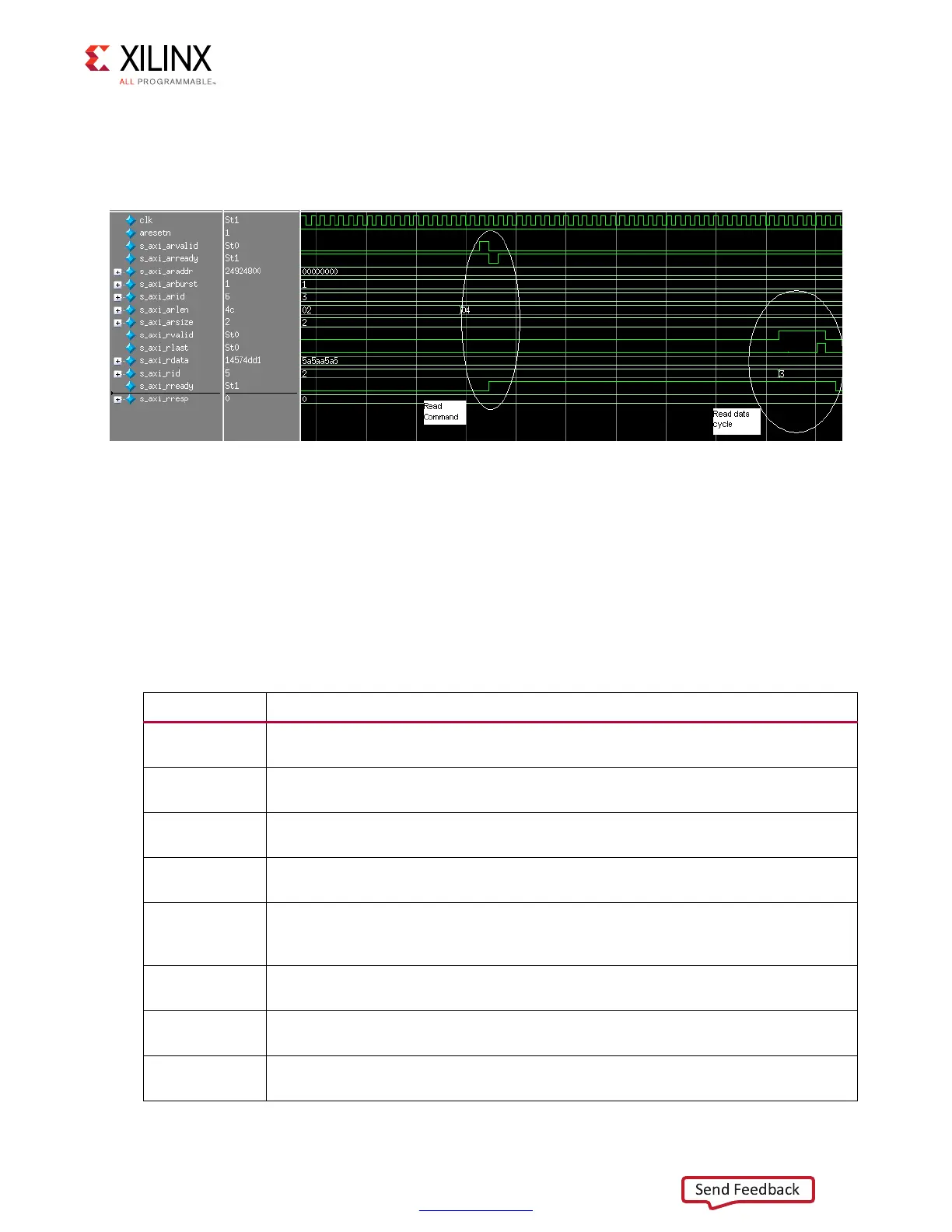

Figure 1-43 shows a simple read transaction being performed on the AXI4 interface. This

transaction consists of a command phase and data phase. This follows the standard AXI4

protocol.

The example design generated when the AXI4 interface is selected as the user interface is

different compared to the standard traffic generator user interface. The intent of this

synthesizable test bench is to verify the basic AXI4 transactions as well as the Memory

Controller transactions. However, this test bench does not verify all Memory Controller

features and is aimed at verifying the AXI4 SHIM features. Table 1-14 shows the signals of

interest during verification of the AXI4 test bench. These signals can be found in the

example_top module.

X-Ref Target - Figure 1-43

Figure 1-43: AXI4 Interface Read Cycle

Table 1-14: Signals of Interest During Simulation for the AXI4 Test Bench

Signal Description

test_cmptd

When asserted, this signal indicates that the current round of tests with random

reads and writes is completed. This signal is deasserted when a new test starts.

write_cmptd

This signal is asserted for one clock indicating that the current write transaction is

completed.

cmd_err

When asserted, this signal indicates that the command phase of the AXI4 transaction

(read or write) has an error.

write_err

When asserted, this signal indicates that the write transaction to memory resulted in

an error.

dbg_wr_sts_vld

When asserted, this signal indicates a valid status for the write transaction on the

dbg_wr_sts bus. This signal is asserted even if the write transaction does not

complete.

dbg_wr_sts

This signal has the status of the write transaction. The details of the status are given

in Table 1-15.

read_cmptd

This signal is asserted for one clock indicating that the current read transaction is

completed.

read_err

When asserted, this signal indicates that the read transaction to the memory resulted

in an error.

Loading...

Loading...