Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 78

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

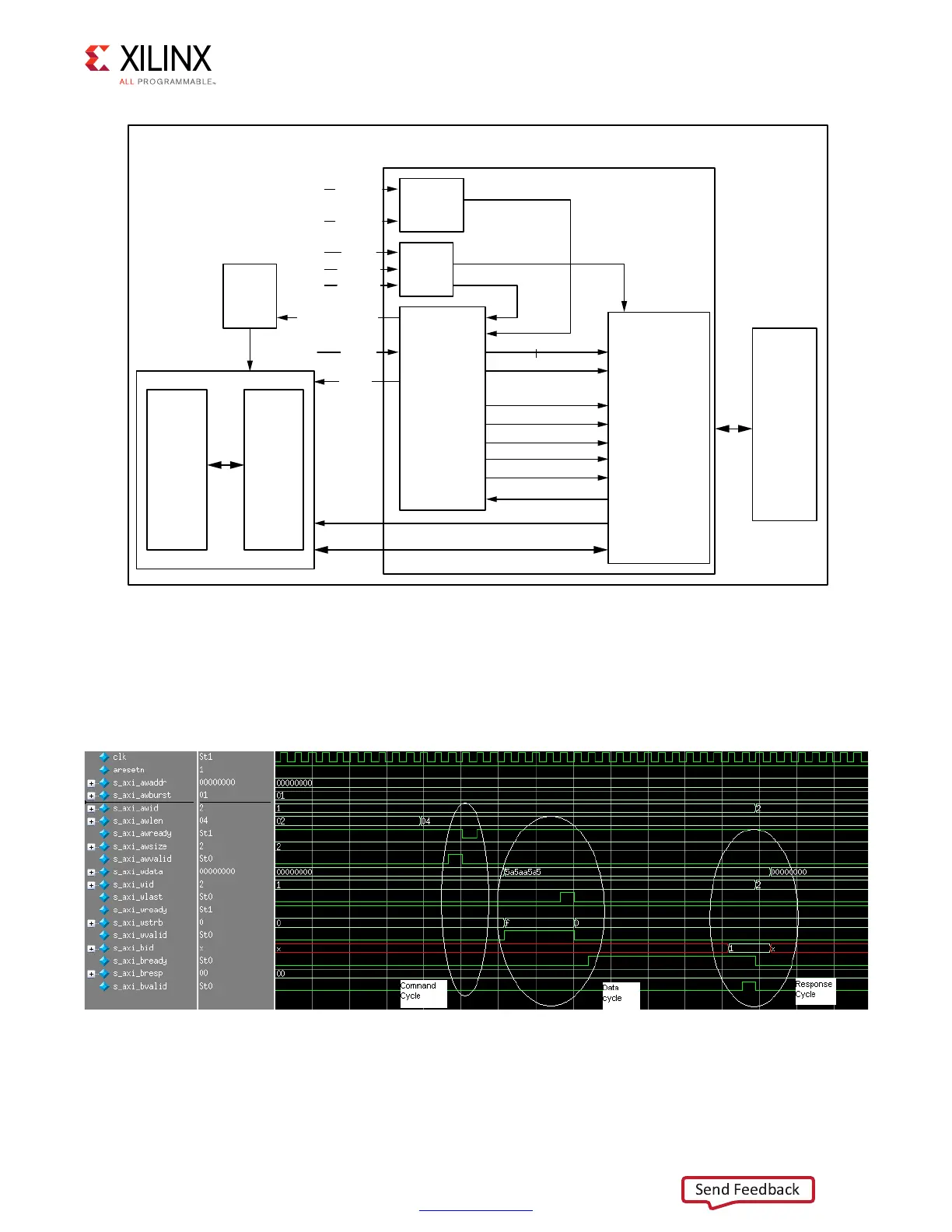

Figure 1-42 shows the simple write transaction being performed on the AXI4 interface. This

transaction consists of a command phase, a data phase, and a response phase. This follows

the standard AXI4 protocol.

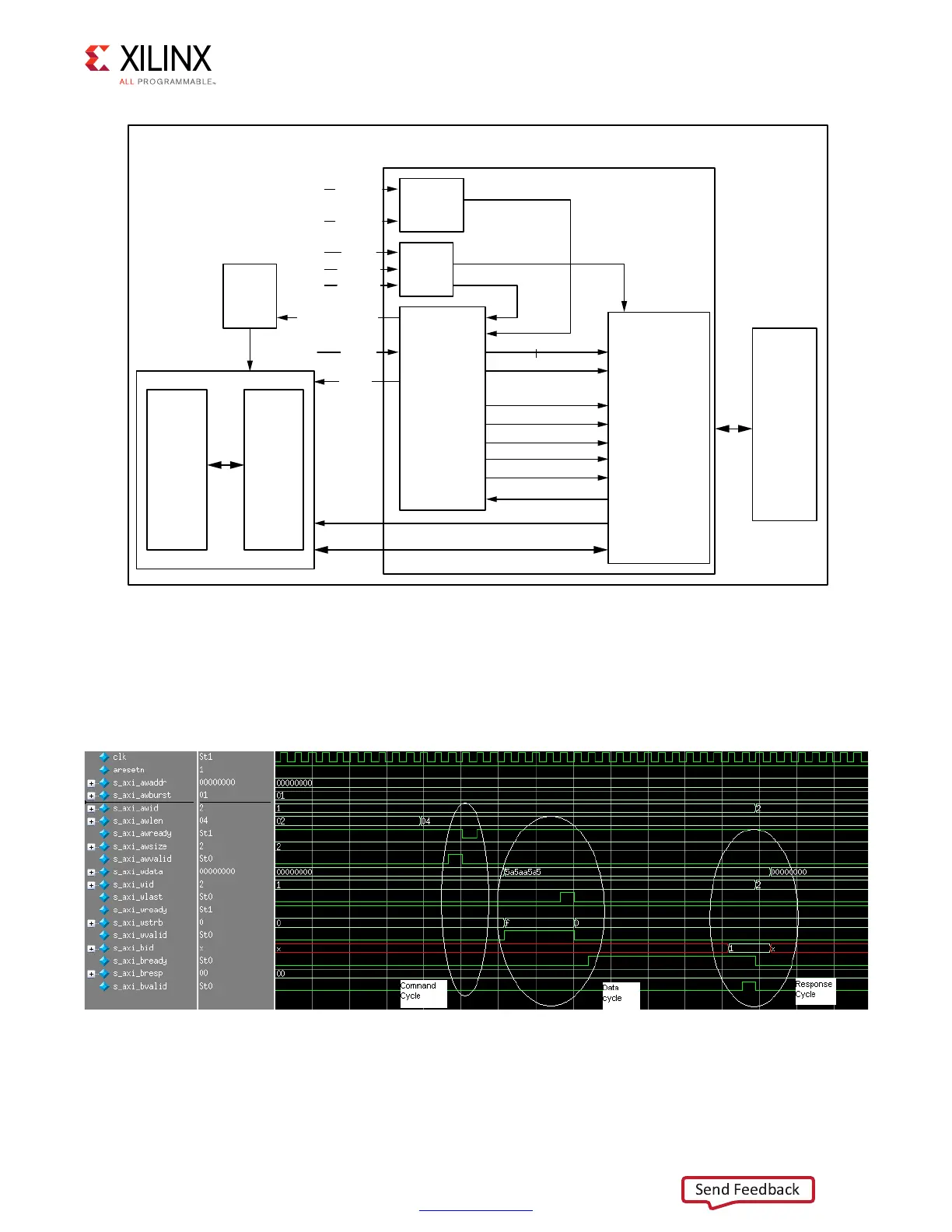

X-Ref Target - Figure 1-41

Figure 1-41: Synthesizable Example Design Block for AXI4 Interface

$$2X

-EMORY

AXI? TG

MEMC ?UI?TOP ?AXI

#ONTROLLERWITH

!8)INTERFACE

0(9

INFRASTRUCTURE

53%2?$%3)'.COMPONENT

MIG ?SERIES ?VX?X

SYS ?CLK ?P

SYS ?CLK ?N

CLK ?IBUF

!8)$ATAAND#ONTROL0ORTS

!8)

7RAPPER

4RAFFIC

'ENERATOR

IODELAY ?

CTRL

CLK ?REF ?N

CLK ?REF ?P

SYS ?RST

CLK ?REF)$%,!9#42,

IODELAY ?CTRL ?RDY

SYS ?RST

MMCM ?CLK

RST

CLK &ABRIC 0(9LOGIC

MEM?REFCLK

FREQ ?REFCLK

RST ?PHASSR ?REF

SYNC ?PULSE

PLL ?LOCKED

REF?DLL ?LOCK

INIT ?CALIB ?COMPLETE

UI?CLK

ARESETN

!8)234

,OGIC

UI?CLK ?SYNC ?RST

8

X-Ref Target - Figure 1-42

Figure 1-42: AXI4 Interface Write Cycle

Loading...

Loading...