Reference Manual ADuCM356

USE CASE CONFIGURATIONS

analog.com Rev. A | 156 of 312

Step 2: Measure R

LOAD02

and External Sensor

(R

SENSOR

)

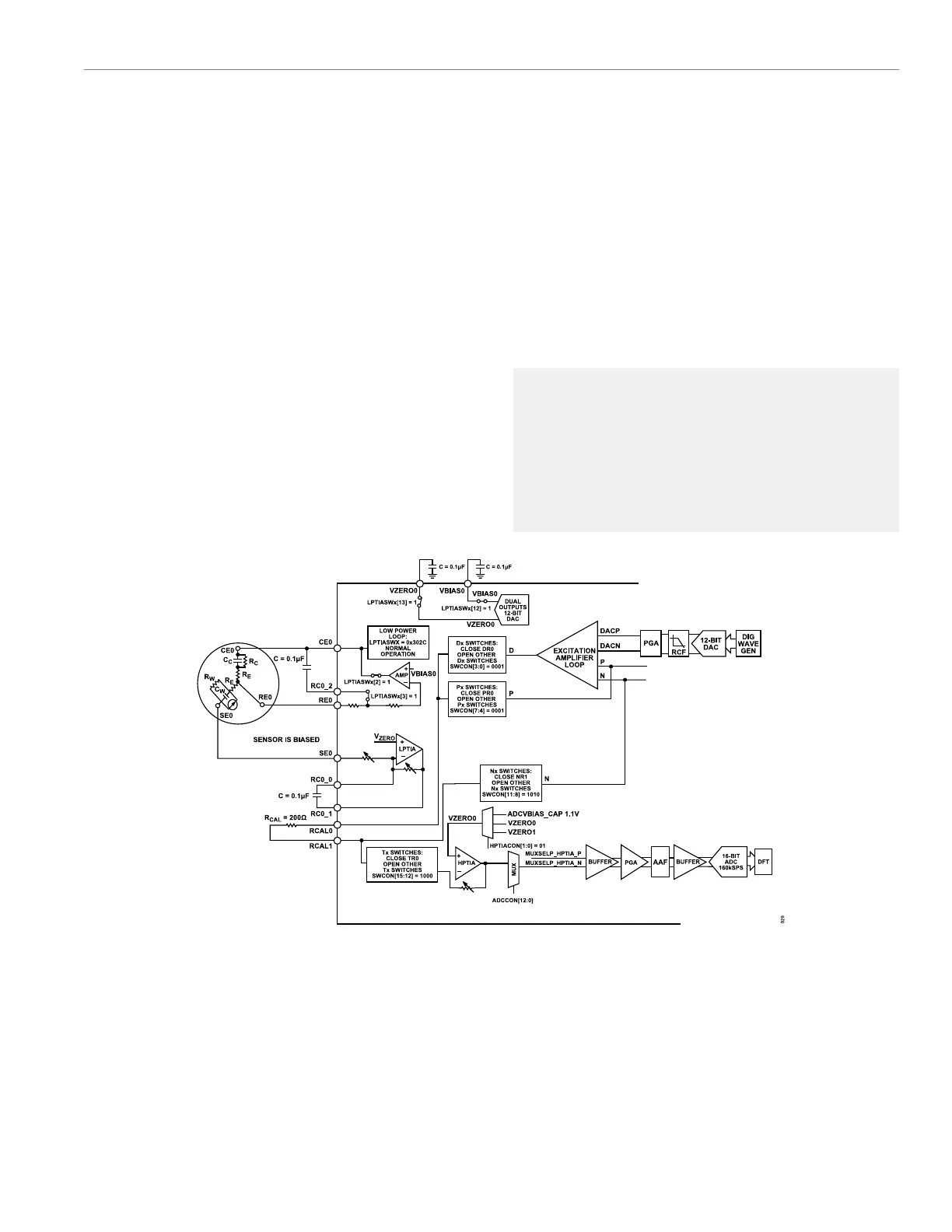

The electrochemical sensor remains biased during this step, but the

working electrode voltage is set by the high-speed TIA instead of

the low-power TIA.

The R

LOAD02

is a fixed value load resistor (100 Ω). In Figure 41,

the reference electrode is the sensor impedance. The waveform

generator and the high-speed DAC generate a 10 mV amplitude

sine waveform on the DC bias voltage that is required for the

reference electrode and the sensing electrode sensor nodes. DACN

is the bias voltage input to the excitation loop from the high-speed

DAC. The sine wave generated by the high-speed DAC is added

at the DACP node. N, P, DACN, and DACP are four inputs of the

excitation amplifier. The differential voltage between the P node and

the N node is the same as the differential voltage between DACP

and DACN.

The sensor is biased, meaning that the required DC voltage is

applied between the reference electrode and the working electrode.

The AC signal is added to the sensor, and the DC bias voltage

is also maintained. The D node provides the correct voltage and

current. As such, the stimulus sine waveform is added between

the electrochemical sensor reference electrode and the high-speed

TIA input. The reference electrode + R

LOAD02

is included in this

AC excitation loop. At this point, the high-speed TIA output is

measured via the ADC signal chain. The programmed number of

ADC samples are fed to the DFT block, which outputs a complex

number (real or imaginary) that reflects the DFT result for the

ADC measurements of the reference electrode + R

LOAD02

. By using

the RCAL impedance measurement result determined after Step 4

and ratiometric measurements, it is possible to obtain an accurate

reference electrode + R

LOAD02

impedance value.

Configure the Tx, Dx, Nx, and Px switches appropriately, as per the

following example code:

AfeS►

witchDPNT(SWID_D5_CE0,SWID_P5_RE0,SWID_N5_SE0RL

OAD,SWID_T5_SE0RLOAD|SWID_T9);

// Connect Excitation Amplifier D to the LP

// Connect Excitation Amplifier P to RE0

// Connect Excitation Amplifier N to SE0 via

RLOAD02

// Connect HSTIA to SE0 via RLOAD02. Close T9

Figure 41. Step Three of Impedance Measurement, R

LOAD02

+ R

SENSOR

Measurement

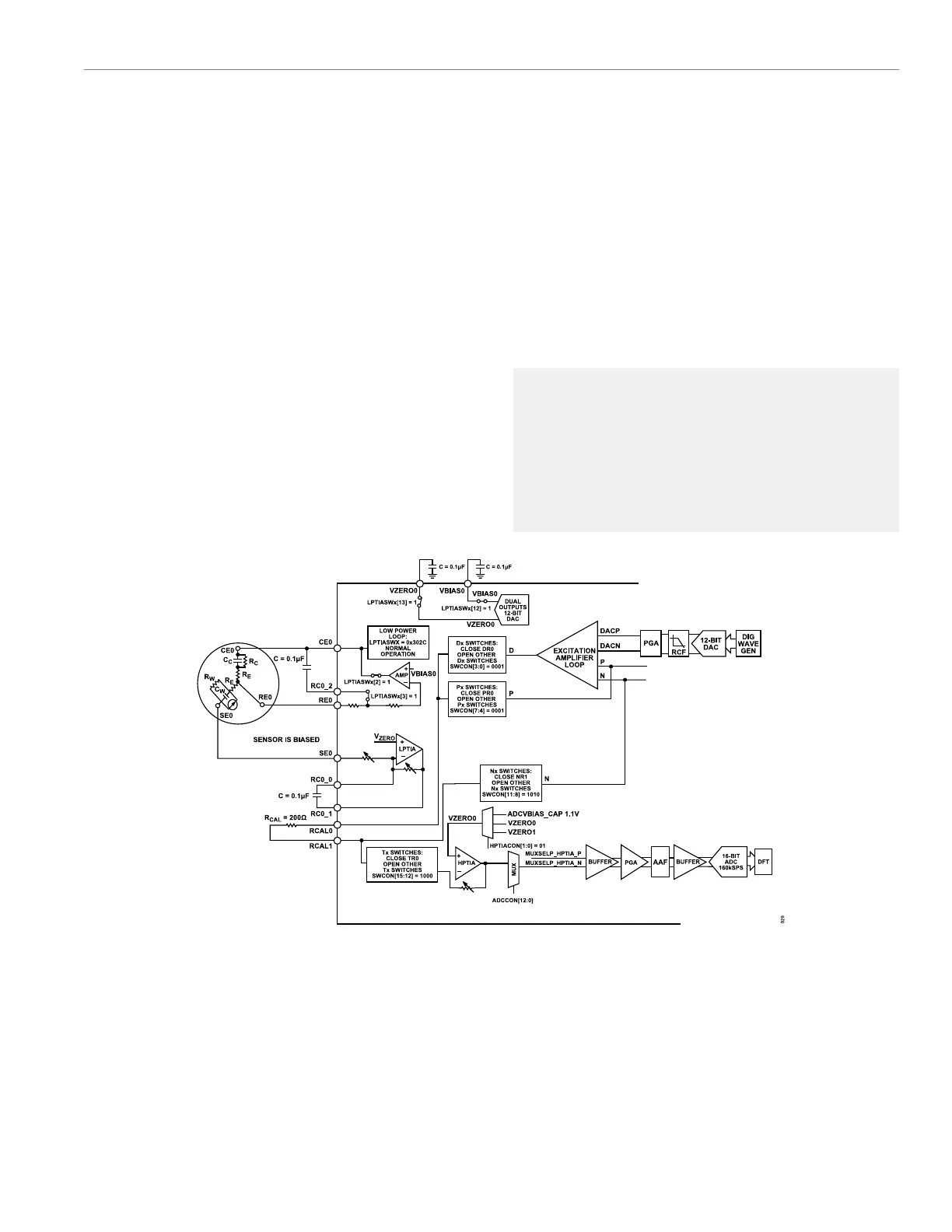

Step 3: Measure R

LOAD02

The counter electrode and reference electrode of the electrochem-

ical sensor are floating during this stage of the measurement

sequence.

The main differences between Step 2 and Step 3 are as follows:

► The reference electrode is disconnected from the excitation

amplifier P node.

► The counter electrode is disconnected from the excitation amplifi-

er D node and is connected directly to R

LOAD02

.

► The excitation amplifier D node is connected to the working

electrode node.

Therefore, the excitation signal is applied to R

LOAD02

and the

sensor is floating, as shown in Figure 42. The AC excitation loop D

node, P node, and R

LOAD02

are shorted. The AC excitation loop N

node, TIA T node, and R

LOAD02

are shorted. Measure the stimulus

Loading...

Loading...