HIGH DATA RATE RECEIVER

HDR-4G+ USER’S MANUAL

Ref. DTU 100782

Is.Rev 3.5

Date: June 1, 2021

© Safran Data Systems – IMP000074 e14r1

This document is the property of Safran Data Systems.

It cannot be duplicated or distributed without expressed written consent.

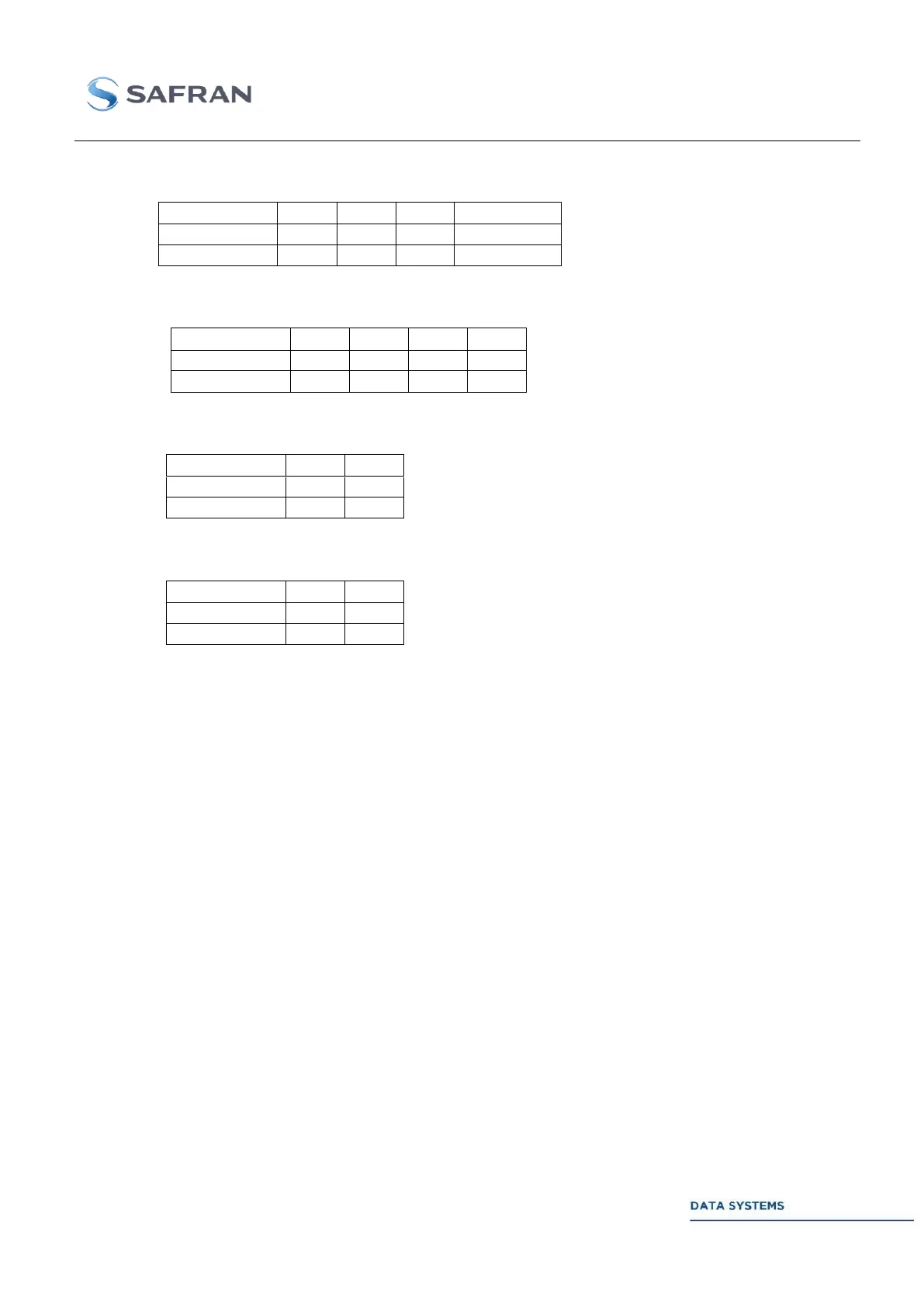

QPSK – 4 DPU, DPU Map = 0

QPSK – 4 DPU, DPU Map = 1

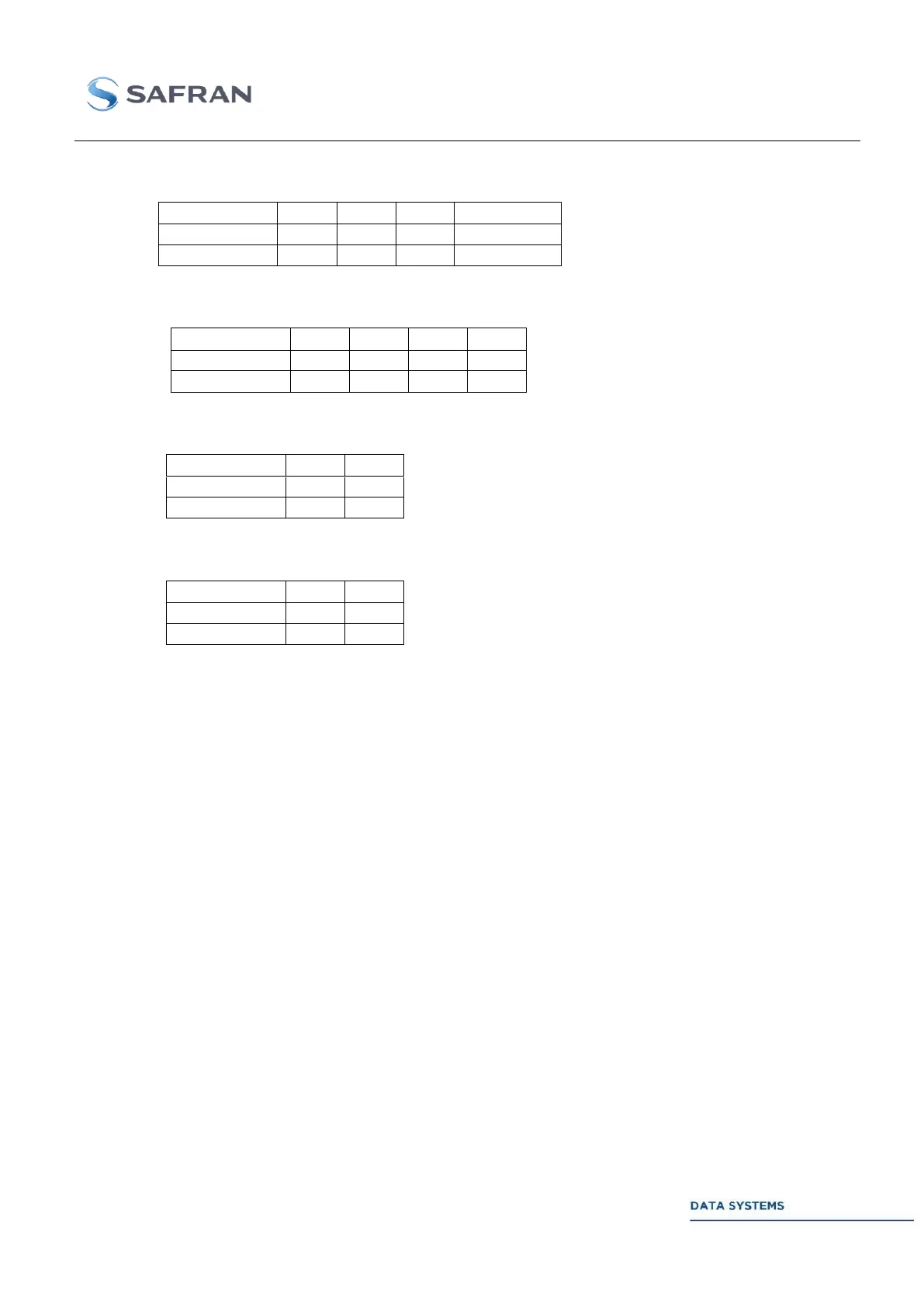

QPSK – 2 DPU, DPU Map = 0 (No ambiguity resolution process)

QPSK – 2 DPU, DPU Map = 1

BER measurements 3.4.13.3

The BER can be done at the DMU (Demodulator Unit) outputs and at each DPU (Data Processing)

output. The BER can be done at different levels inside the DPU by enabling or not the different

operations (Differential encoder/decoder, Frame synchronizer, CCSDS encoder/decoder).

Loading...

Loading...