HIGH DATA RATE RECEIVER

HDR-4G+ USER’S MANUAL

Ref. DTU 100782

Is.Rev 3.5

Date: June 1, 2021

© Safran Data Systems – IMP000074 e14r1

This document is the property of Safran Data Systems.

It cannot be duplicated or distributed without expressed written consent.

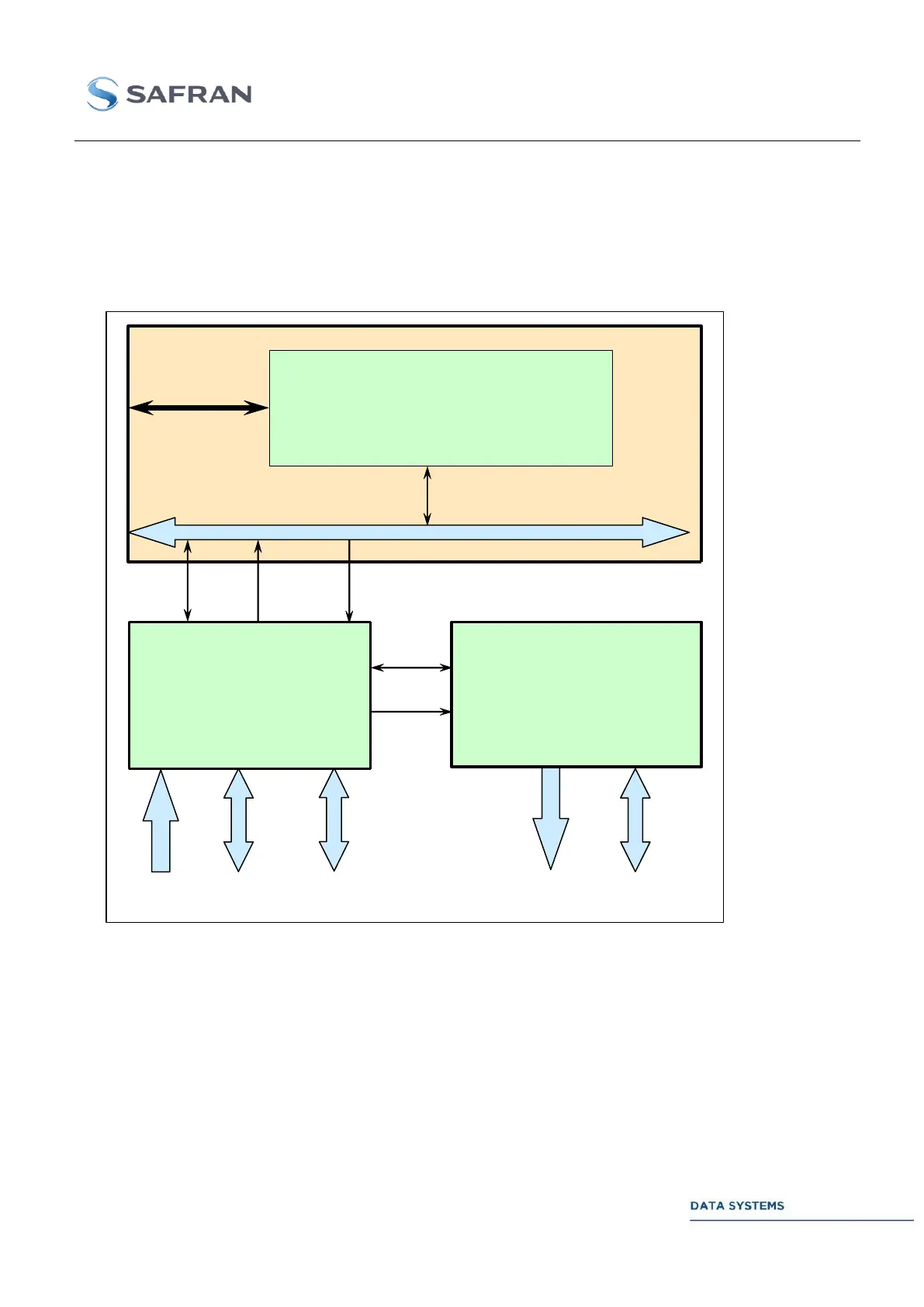

CORTEX HDR Hardware Architecture 1.4.3

The CORTEX HDR comprises the following elements:

A PC-compatible workstation,

A Demodulator board (SDSY),

An optional Test Modulator board, including a noise generator and a telemetry simulator

(SDSY).

ETHERNET PORT

PC Server Board

PCI BUS

Demodulator Board

Test Modulator Board

(Option)

TM DataMonitoring

& Control

Playback

Data

PC-compatible Workstation

IF

INPUTS

PCM + CLOCK

I/Os

IF

OUTPUT

TEST

I/Os

Playback Data

10M + IRIG+AGC

I/Os

Monitoring

& Control

Figure 4: CORTEX HDR Hardware Block Diagram

Loading...

Loading...