HIGH DATA RATE RECEIVER

HDR-4G+ USER’S MANUAL

Ref. DTU 100782

Is.Rev 3.5

Date: June 1, 2021

© Safran Data Systems – IMP000074 e14r1

This document is the property of Safran Data Systems.

It cannot be duplicated or distributed without expressed written consent.

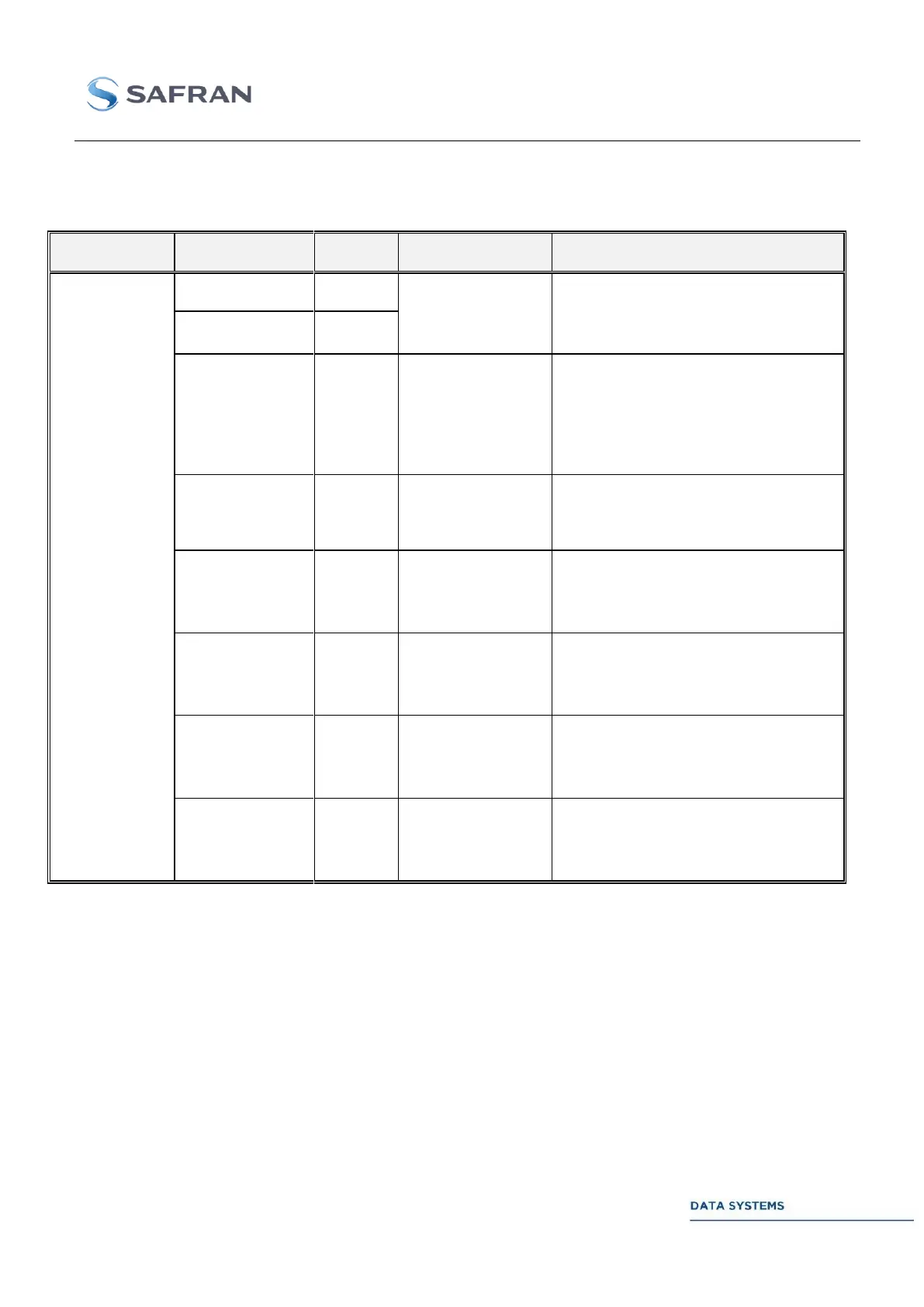

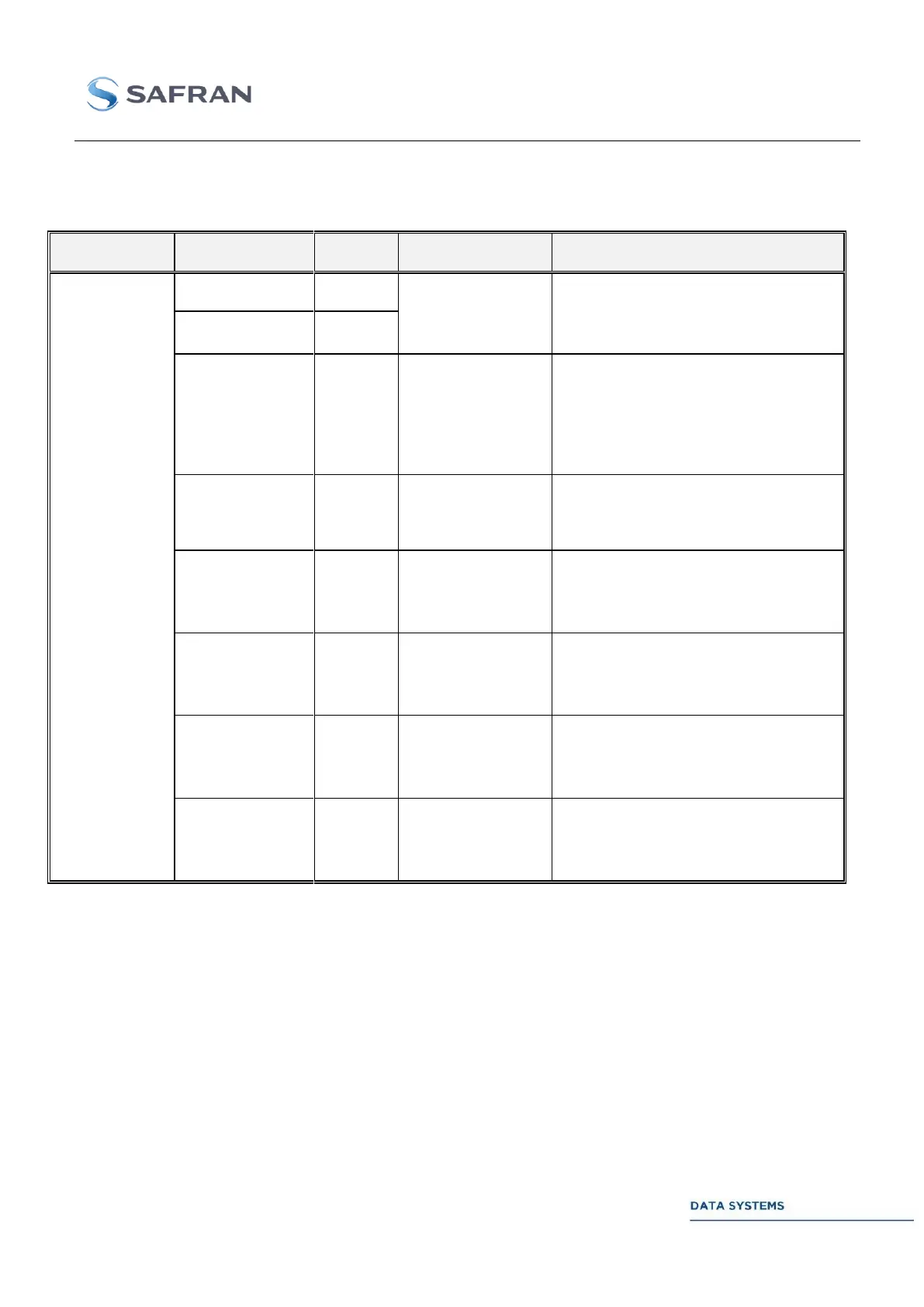

Test Modulator I/Os 2.2.2.3

All I/O connectors are SMA:

Single ended ECL

> -0.81 V for high level

< -1.95 V for low level

ECL termination -2V, 56 included

(Not used in this version)

10 MHz, sine or square, 50

0.5 to 10 Vpp (if DC = 0)

DC max = 4 V

IF Input of test mod

Up-converter 1

Optional

IF Input of test mod

Up-converter 2

Optional

IF Output of test mod

Up-converter 1

Optional

IF Output of test mod

Up-converter 2

Optional

Table 9: Modulator I/Os Definition

Loading...

Loading...