Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 187

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

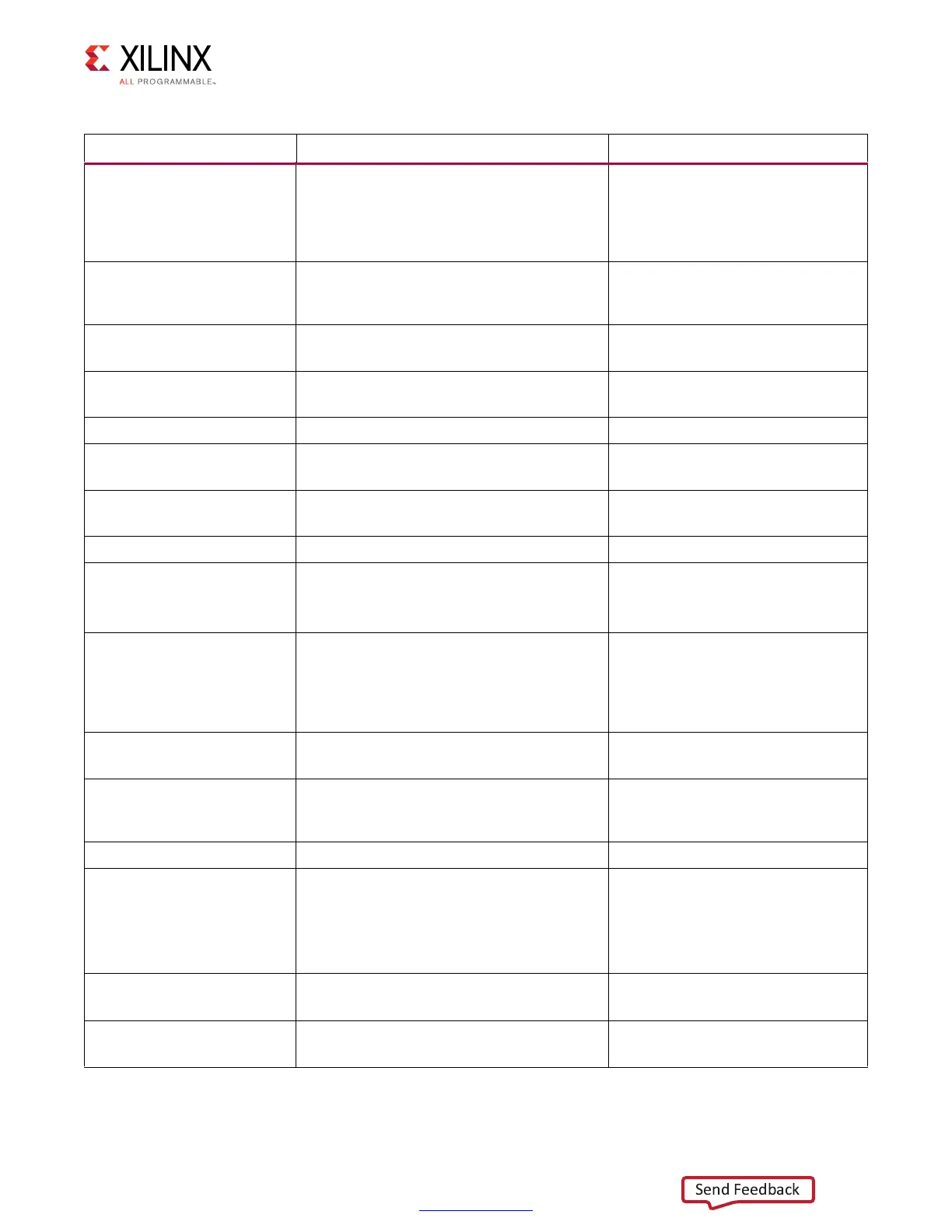

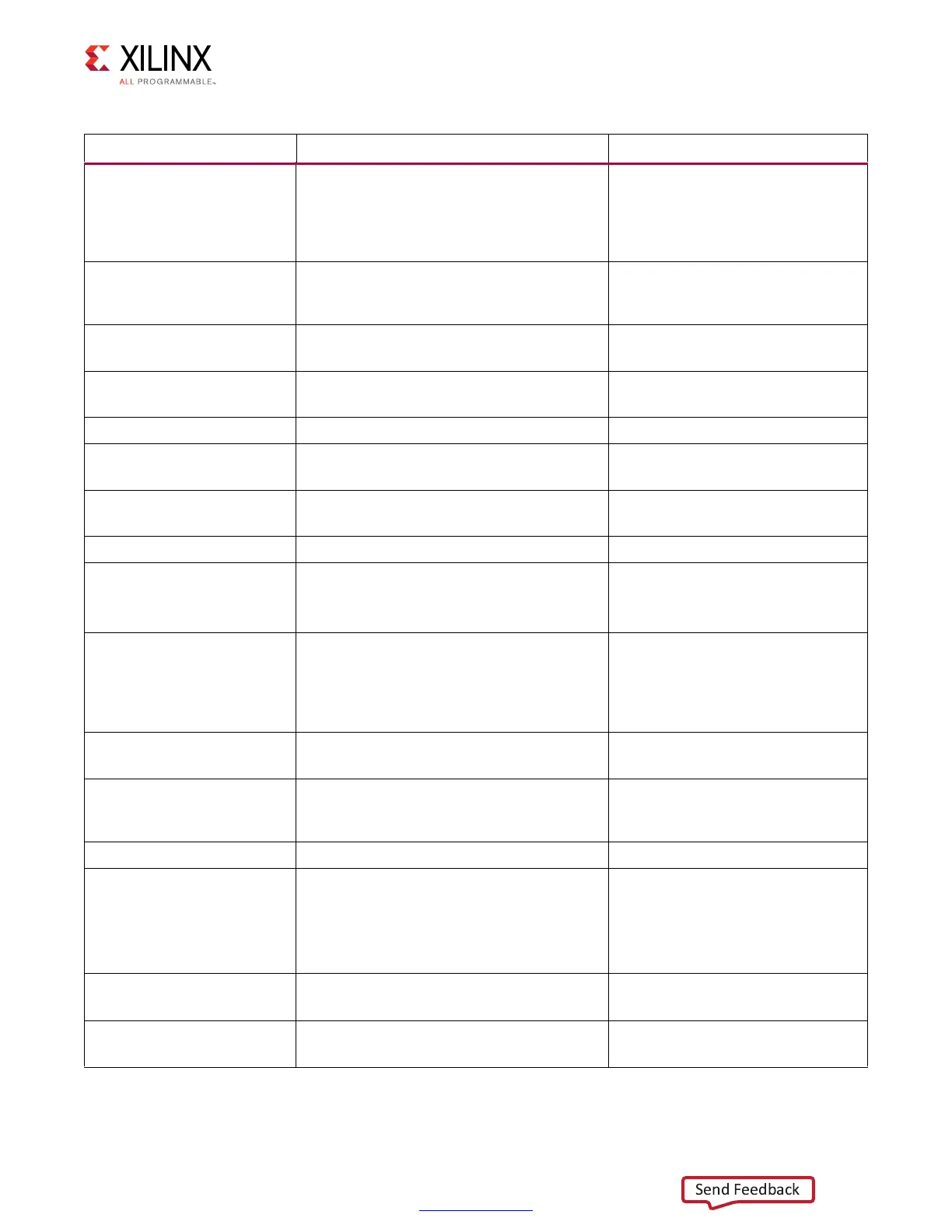

CLKOUT0_PHASE –

Phase of PLL output CLKOUT0. This

value is set by the MIG tool based

on the banks selected for memory

interface pins and the frequency of

operation.

DIVCLK_DIVIDE –

PLLE2 VCO divisor. This value is set

by the MIG tool based on the

frequency of operation.

USE_DM_PORT

This is the enable data mask option used

during memory write operations.

0 = Disable

1 = Enable

CK_WIDTH

This is the number of CK/CK# outputs to

memory.

DQ_CNT_WIDTH This is ceil(log2(DQ_WIDTH)).

DRAM_TYPE

This is the supported memory standard for

the Memory Controller.

“DDR3”, “DDR2”

DRAM_WIDTH

This is the DQ bus width per DRAM

component.

AL This is the additive latency. 0

nBANK_MACHS

(1)

This is the number of bank machines. A

given bank machine manages a single

DRAM bank at any given time.

2, 3, 4, 5, 6, 7, 8

DATA_BUF_ADDR_WIDTH

This is the bus width of the request tag

passed to the Memory Controller. This

parameter is set to 5 for 4:1 mode and 4 for

2:1 mode. This parameter should not be

changed.

5, 4

SLOT_0_CONFIG

This is the rank mapping. This parameter

should not be changed.

Single-rank setting: 8'b0000_0001

Dual-rank setting: 8'b0000_0011

ECC

This is the error correction code, available in

72-bit data width configurations. ECC is not

currently available.

72

RANKS This is the number of ranks.

DATA_WIDTH

This parameter determines the write data

mask width and depends on whether or not

ECC is enabled.

ECC = ON:

DATA_WIDTH = DQ_WIDTH +

ECC_WIDTH

ECC = OFF:

DATA_WIDTH = DQ_WIDTH

APP_DATA_WIDTH

This UI_INTFC parameter specifies the

payload data width in the UI.

APP_DATA_WIDTH =

2 x nCK_PER_CLK x PAYLOAD_WIDTH

APP_MASK_WIDTH

This UI_INTFC parameter specifies the

payload mask width in the UI.

Table 1-65: Embedded 7 Series FPGAs Memory Solution Configuration Parameters (Cont’d)

Parameter Description Options

Loading...

Loading...