Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 197

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

• Differential signals should be terminated with the memory device internal termination

or an 80Ω differential termination at the load (Figure 1-93). For bidirectional signals,

termination is needed at both ends of the signal. ODT should be used on the memory

side. For best performance in HP banks, DCI should be used. For best performance in

HR banks, IN_TERM (internal termination) should be used.

Note:

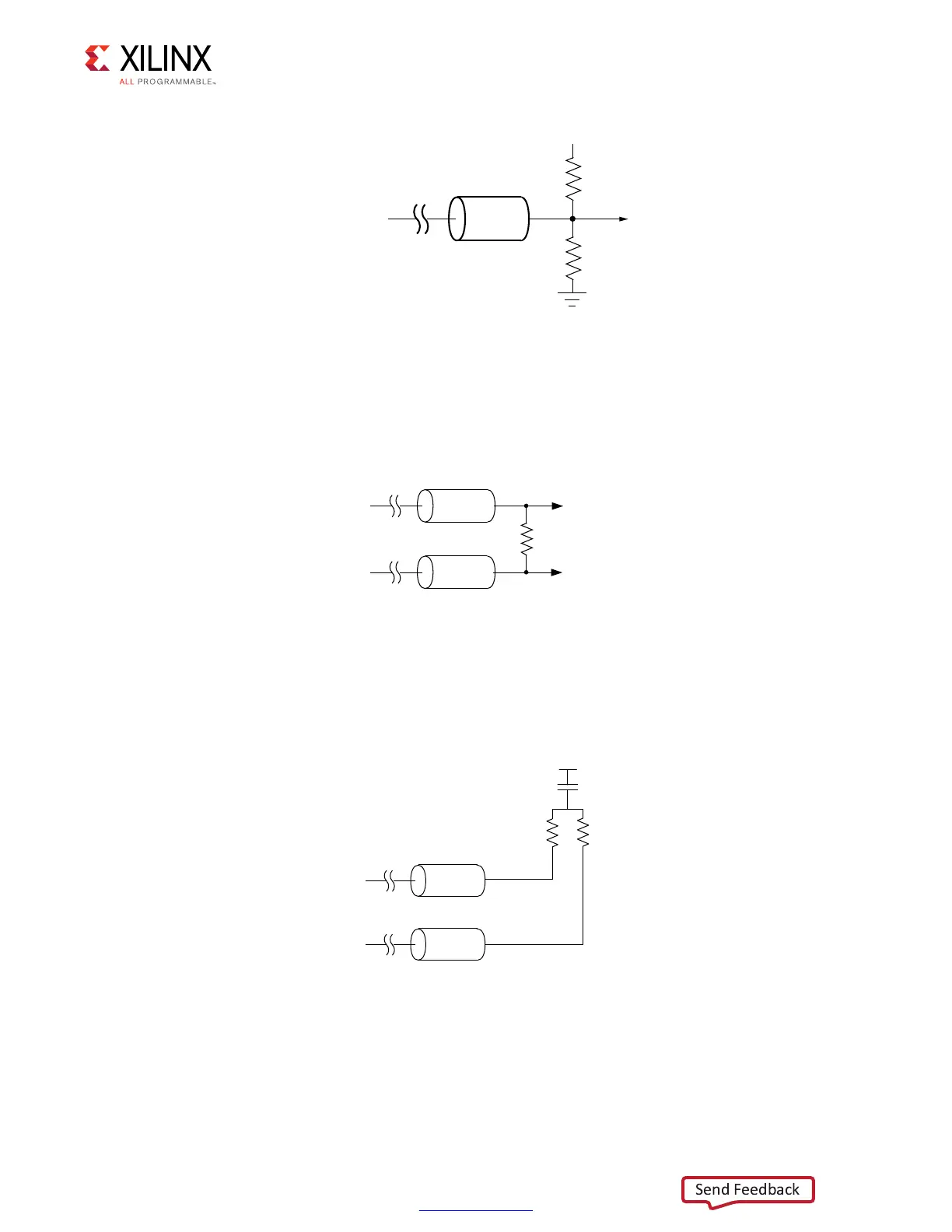

For CK_P/CK_N differential signals, the termination method mentioned in Figure 1-94 is

recommended.

• All termination must be placed as close to the load as possible. The termination can be

placed before or after the load provided that the termination is placed within a small

distance of the load pin. The allowable distance can be determined by simulation.

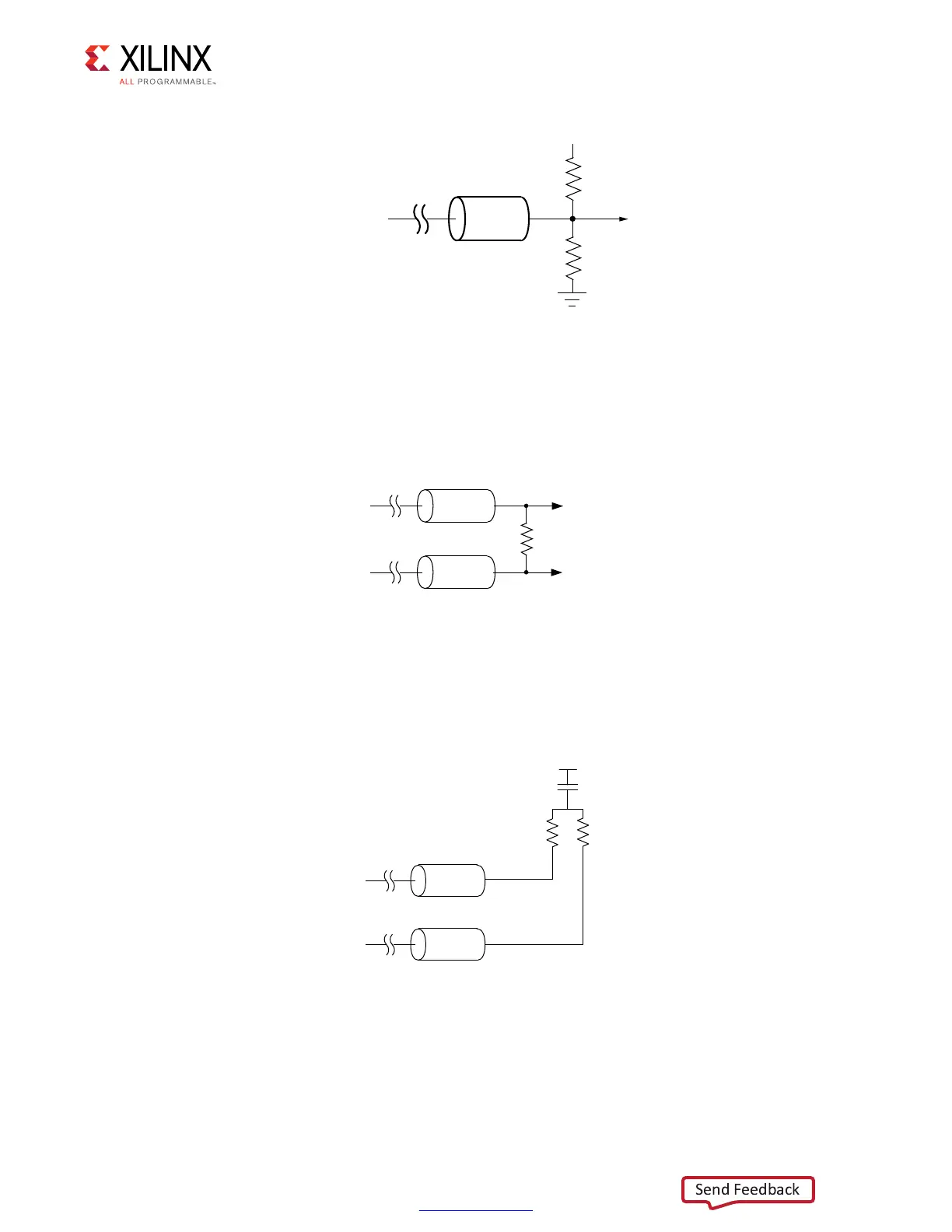

X-Ref Target - Figure 1-92

Figure 1-92: 80Ω Split Termination to V

CCO

and GND

X-Ref Target - Figure 1-93

Figure 1-93: (a) 80Ω Differential Termination

X-Ref Target - Figure 1-94

Figure 1-94: (b) 80Ω Differential Termination

5'?C??

:1

½

X:1

½

X:1

½

6

##/

,OAD3OURCE

ZQ = 40W

2 x ZQ = 80W

Load_PSource_P

ZQ = 40W

Load_N

Source_

N

X16403-091416

ZQ = 40W

R

TT

= 30Ω

Source_P

ZQ = 40W

V

CCO

Source_N

R

TT

= 30Ω

C = 0.1 μF

X16404-091416

Loading...

Loading...