Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 488

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

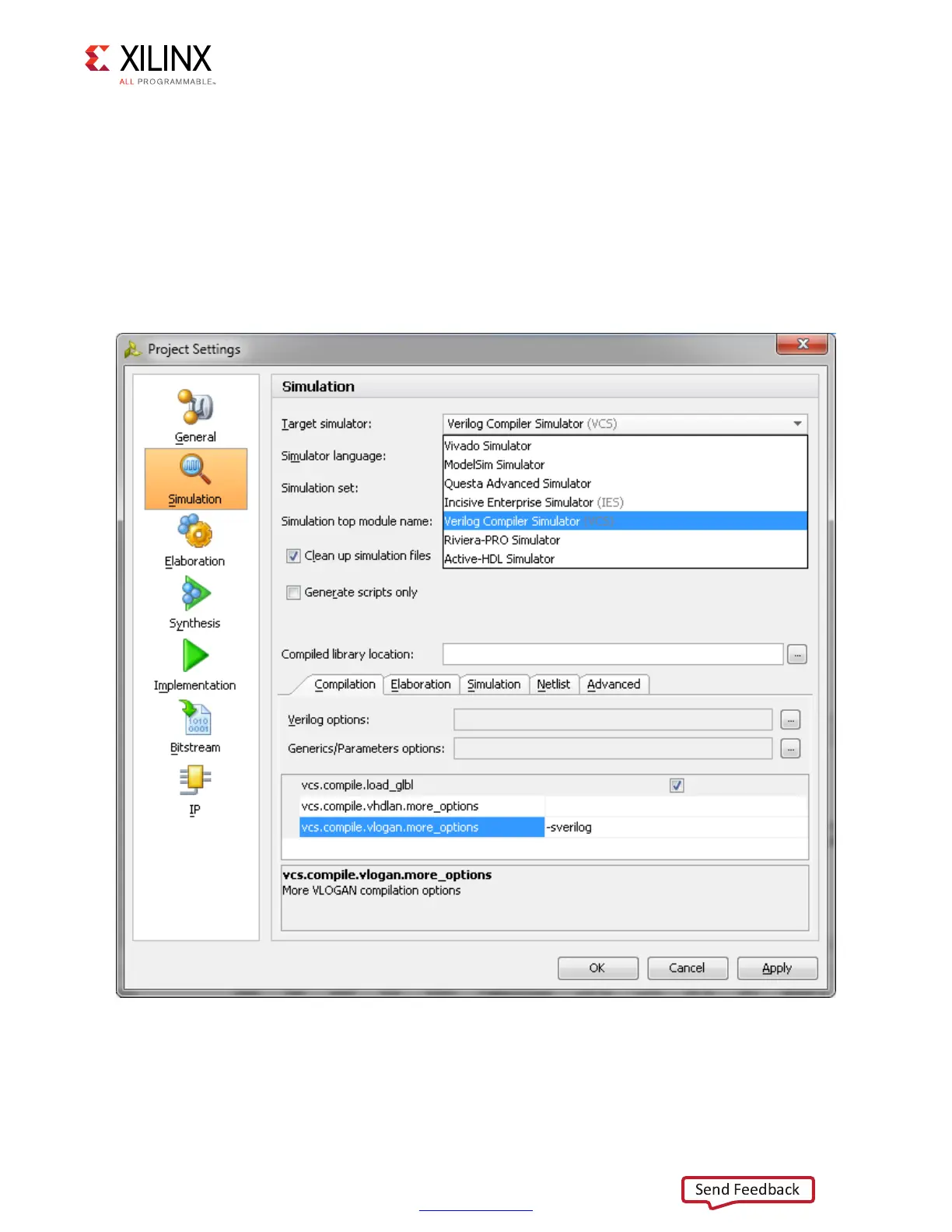

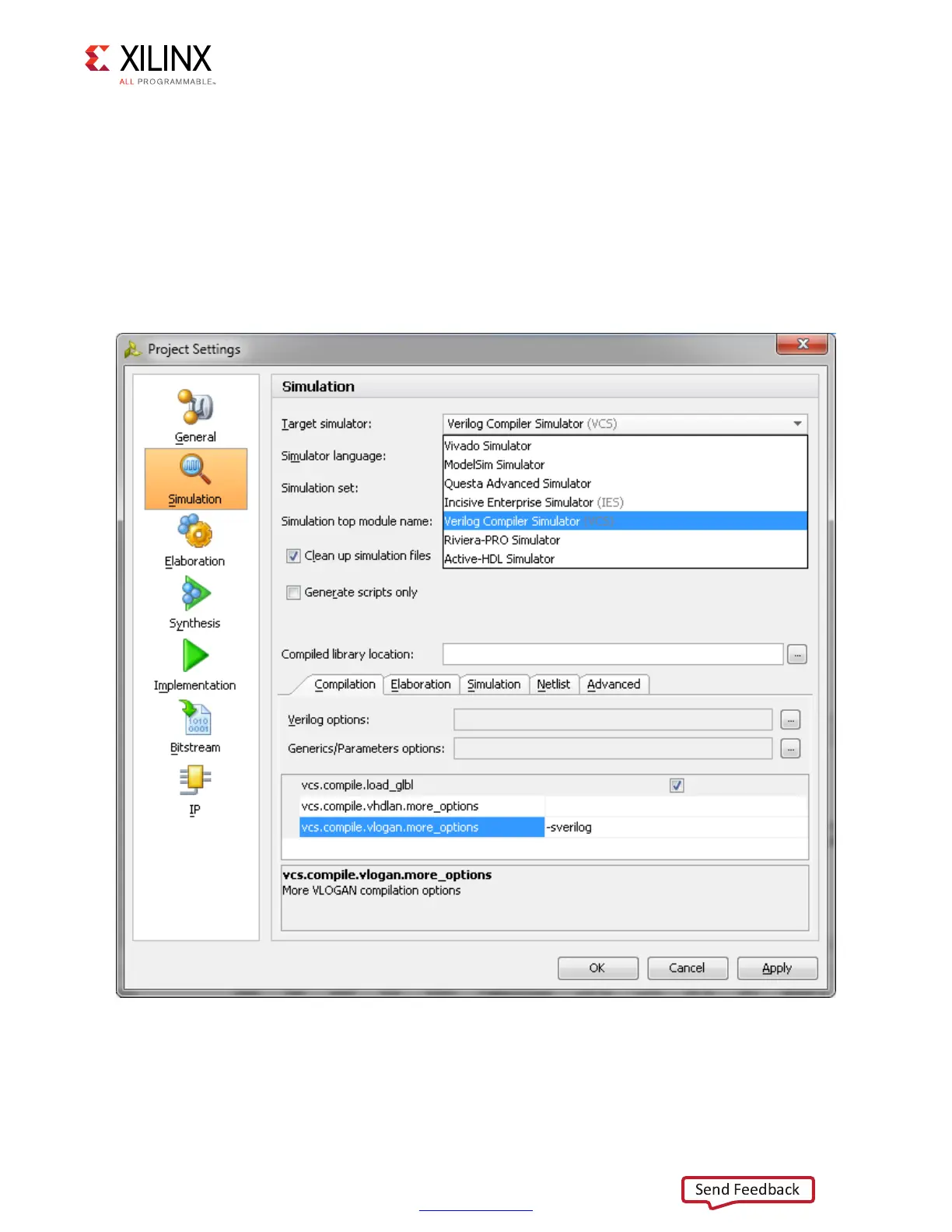

a. Browse to the Compiled libraries location and set the path on Compiles libraries

location option.

b. Under the Compilation tab, set the vcs.compile.vlogan.more_options to

-sverilog.

c. Under the Simulation tab, set the vcs.simulate.runtime to 1 ms (there are

simulation RTL directives which stop the simulation after a certain period of time

which is less than 1 ms) as shown in Figure 3-67.

3. Apply the settings and select OK.

4. In the Flow Navigator window, select Run Simulation and select Run Behavioral

Simulation as shown in Figure 3-65.

X-Ref Target - Figure 3-67

Figure 3-67: Simulation with VCS

Loading...

Loading...