Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 494

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

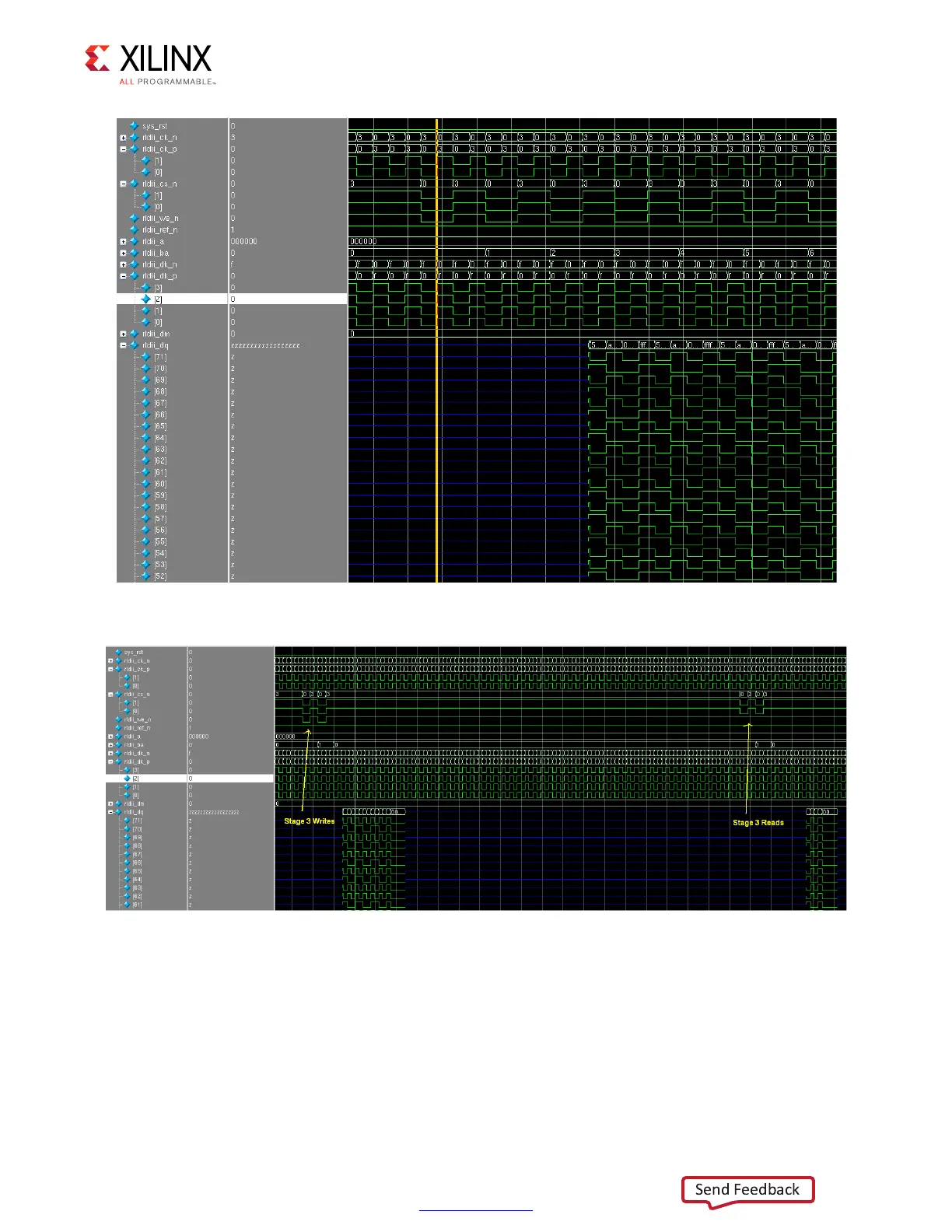

An additional write/read is performed so the read bus is driven to a different value. This is

mostly required in hardware to make sure that the read calibration can distinguish the

correct data pattern.

After the third stage calibration completes, init_calib_complete is asserted, signifying

successful completion of the calibration process.

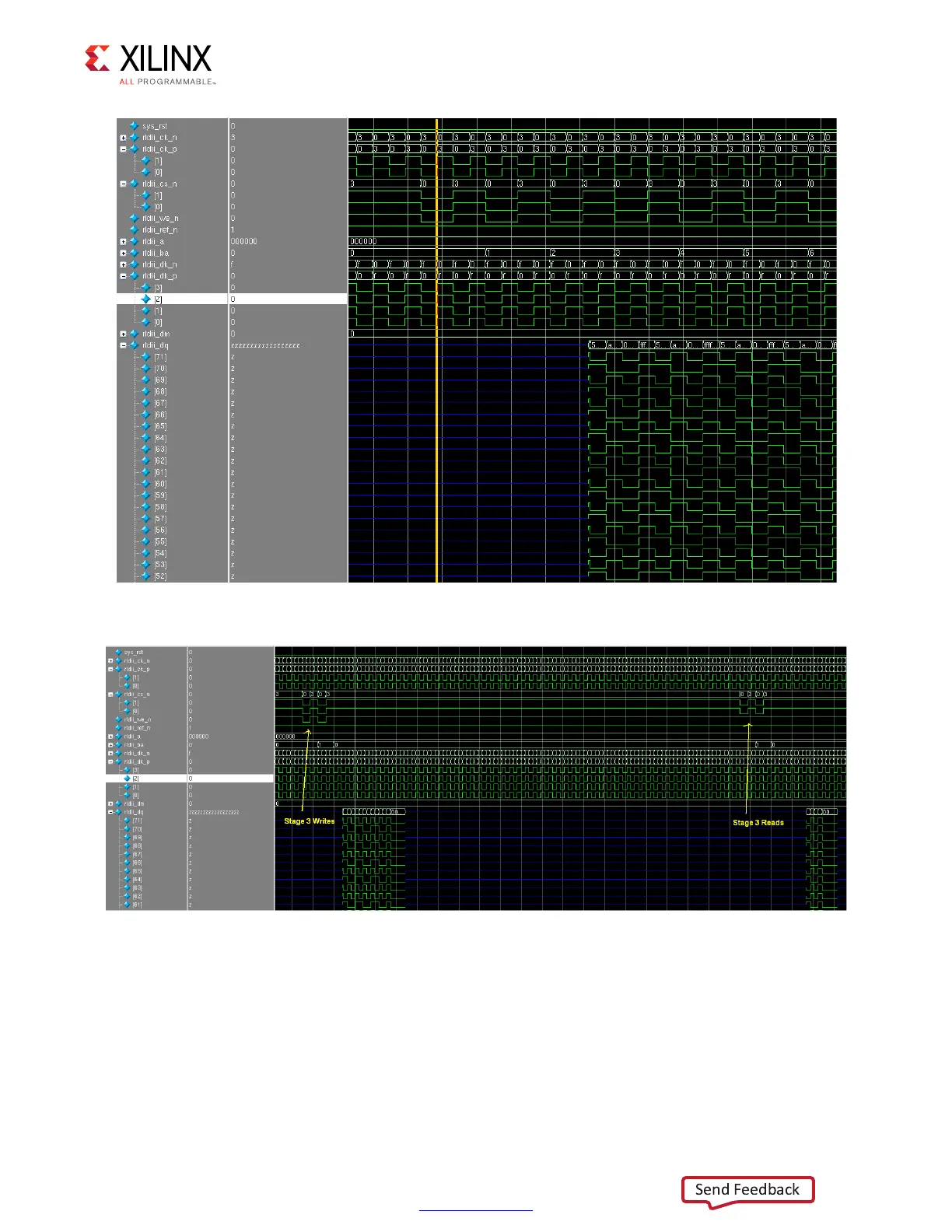

X-Ref Target - Figure 3-71

Figure 3-71: Write and Read for Second Stage Read Calibration (Pattern Shown for RLDRAM II)

X-Ref Target - Figure 3-72

Figure 3-72: Write and Read for Third Stage Read Calibration (Pattern Shown for RLDRAM II)

Loading...

Loading...