Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 496

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

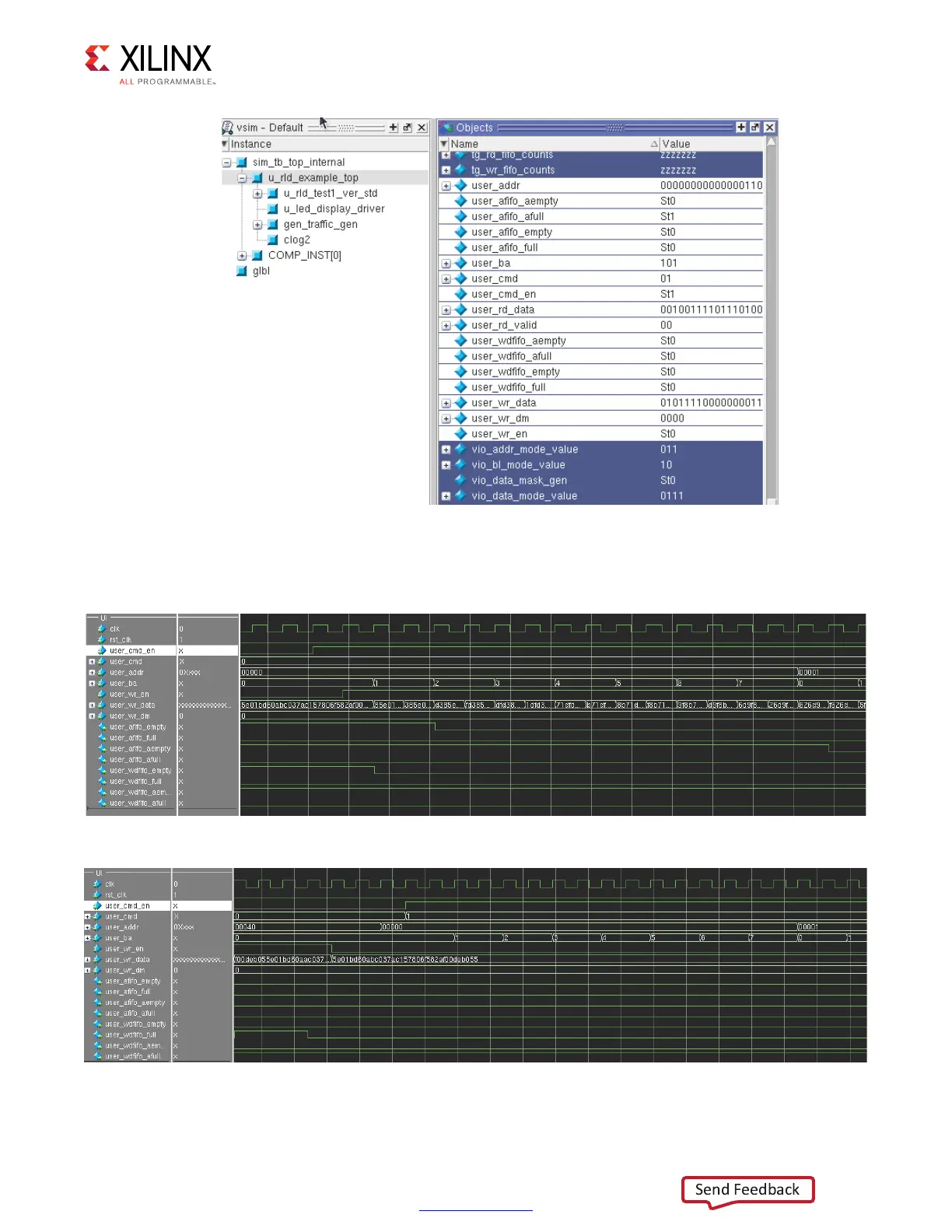

Figure 3-75 and Figure 3-76 show example waveforms of a write and read on both the user

interface.

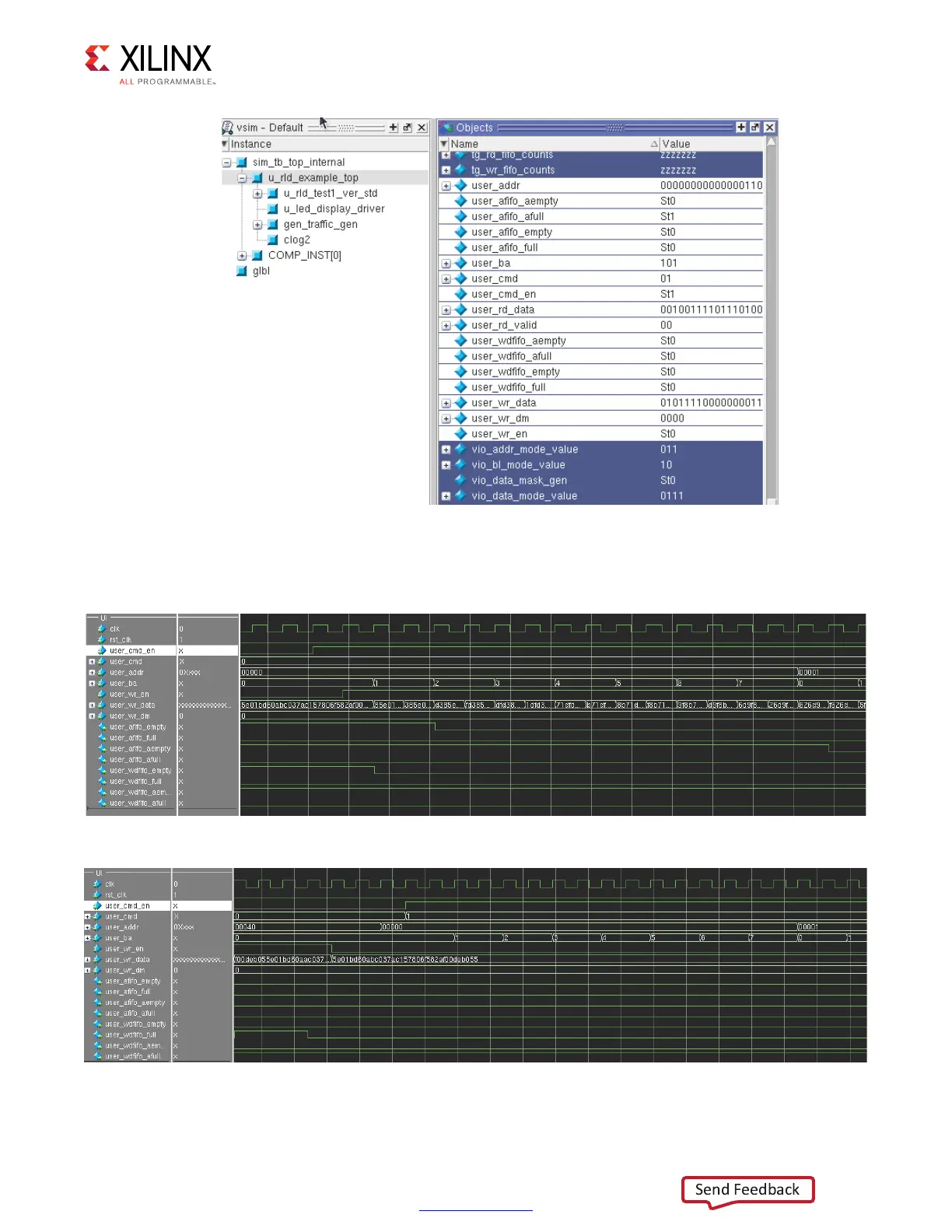

X-Ref Target - Figure 3-74

Figure 3-74: Questa Advanced Simulator Instance Window

X-Ref Target - Figure 3-75

Figure 3-75: User Interface Write

X-Ref Target - Figure 3-76

Figure 3-76: User Interface Read

Loading...

Loading...