Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 673

UG586 November 30, 2016

www.xilinx.com

Appendix A: General Memory Routing Guidelines

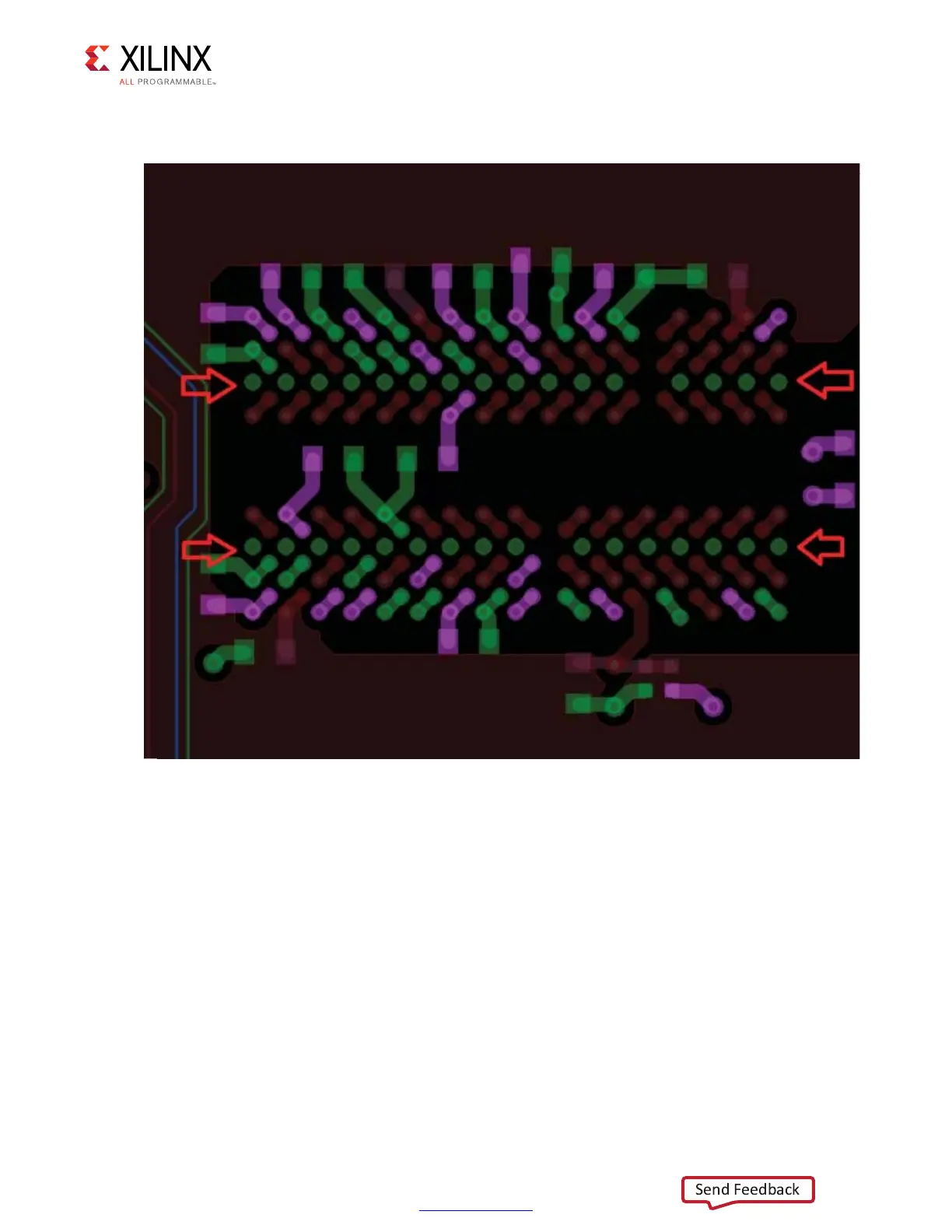

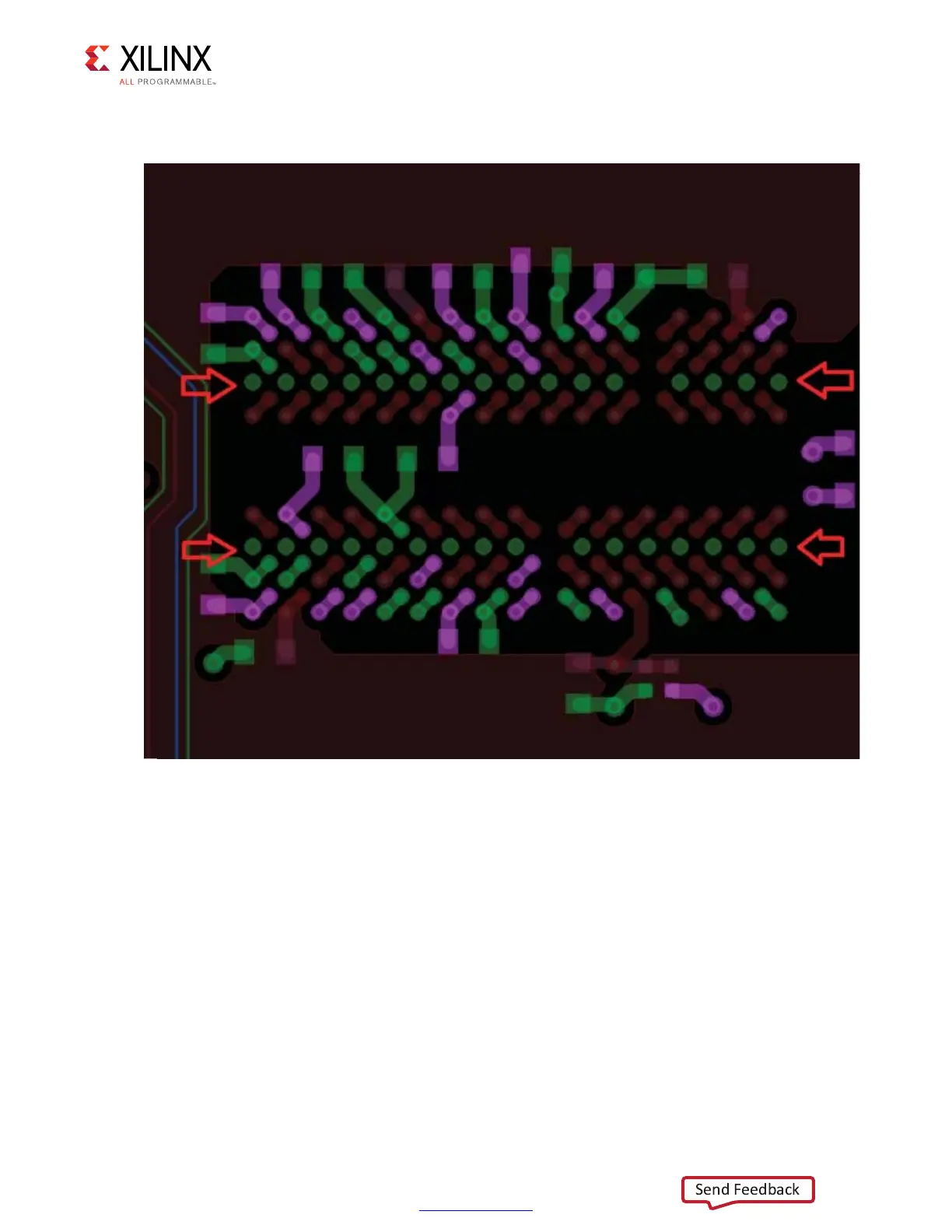

10. Use chevron-style routing to allow for ground stitch vias (Figure A-5).

11. Add ground vias as much as possible around the edges of the device and inside the

device to make a better ground return path for signals and power, especially corners.

Corner or edge balls are generally less populated as grounds.

X-Ref Target - Figure A-5

Figure A-5: Example of Ground Stitching

Loading...

Loading...