Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 674

UG586 November 30, 2016

www.xilinx.com

Appendix A: General Memory Routing Guidelines

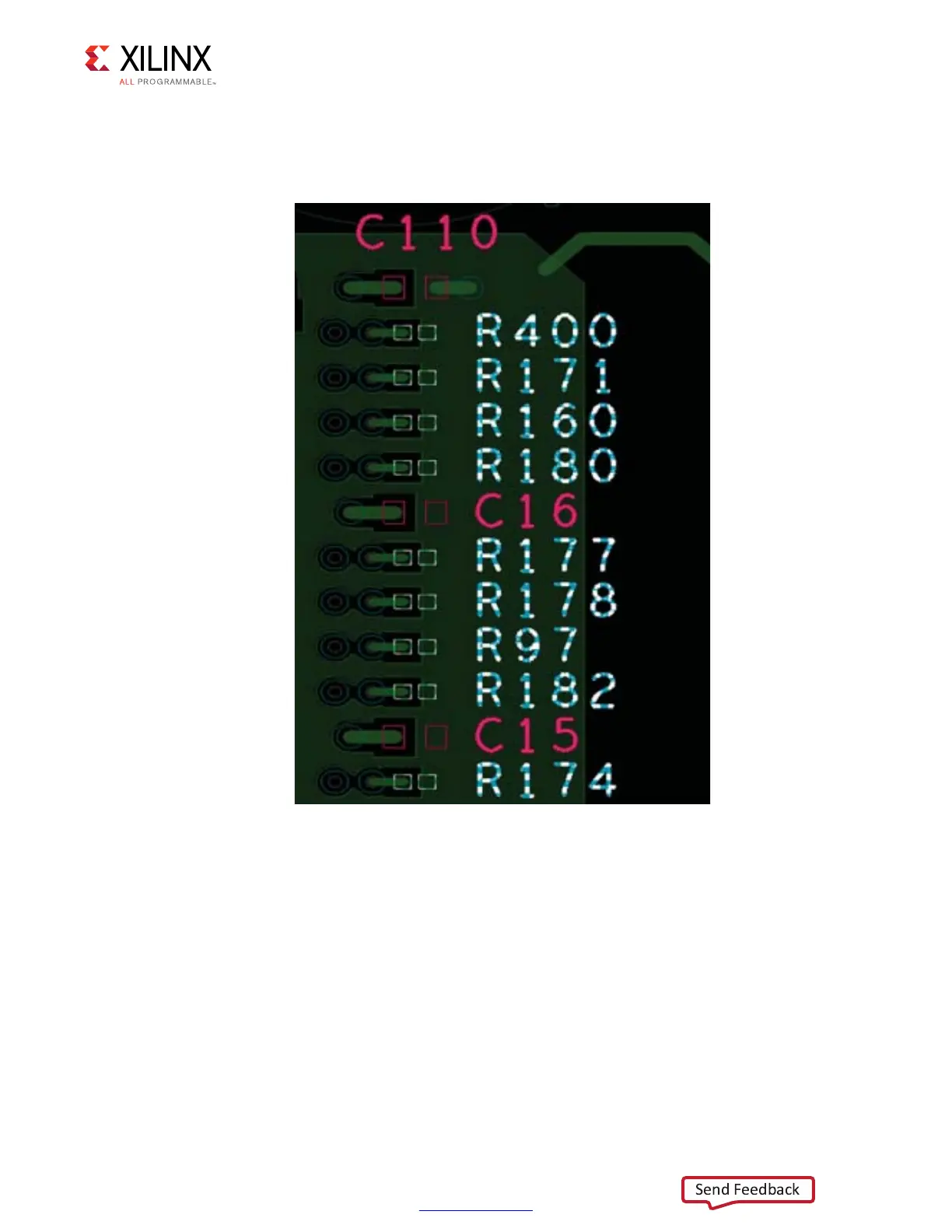

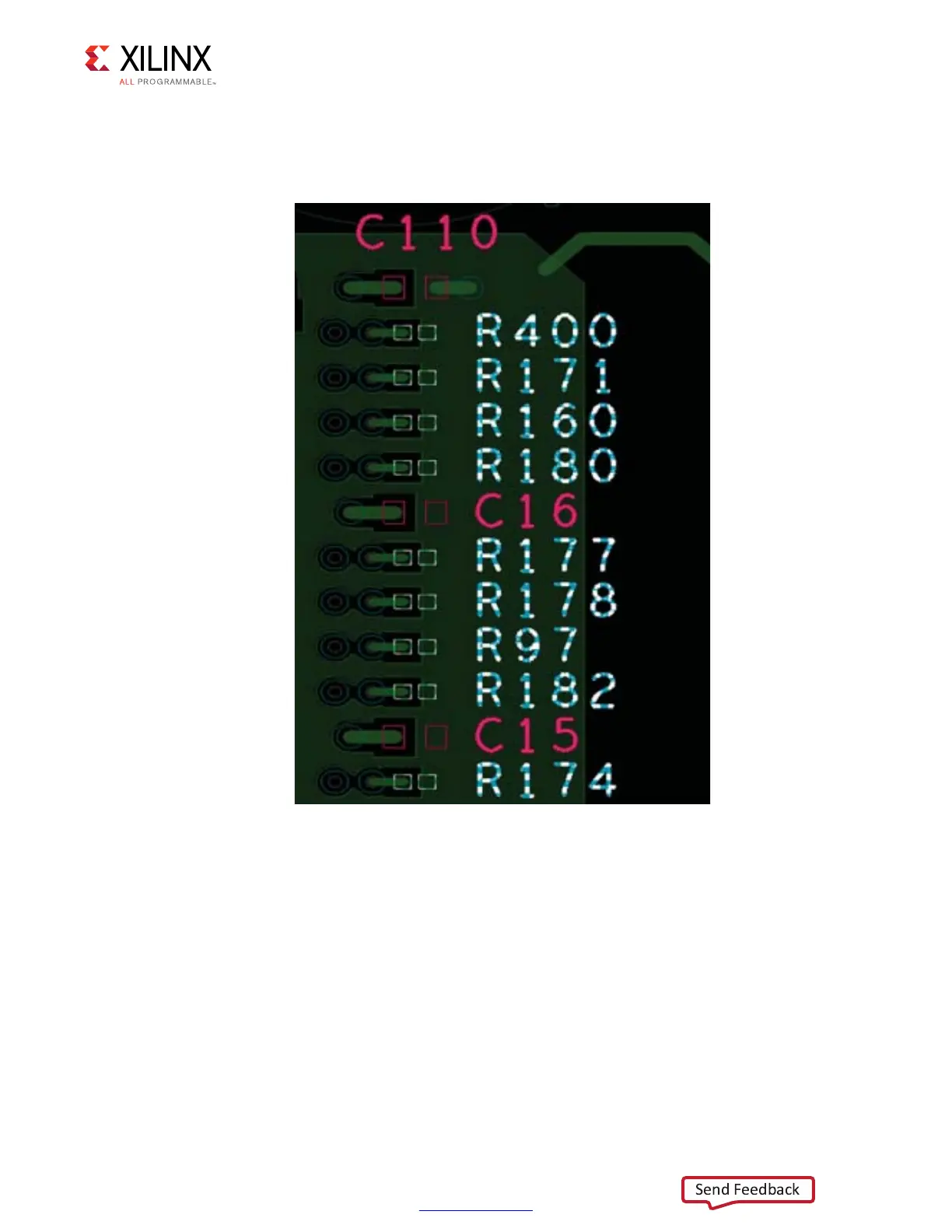

12. For ADDR/CMD/CTRL V

TT

termination, every four termination resistors should be

accompanied by one 1.0 µF capacitor, physically interleaving among resistors, as shown

in Figure A-6.

X-Ref Target - Figure A-6

Figure A-6: Example of V

TT

Termination Placement

UG583_c2_17_050614

Loading...

Loading...