Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 675

UG586 November 30, 2016

www.xilinx.com

Appendix A: General Memory Routing Guidelines

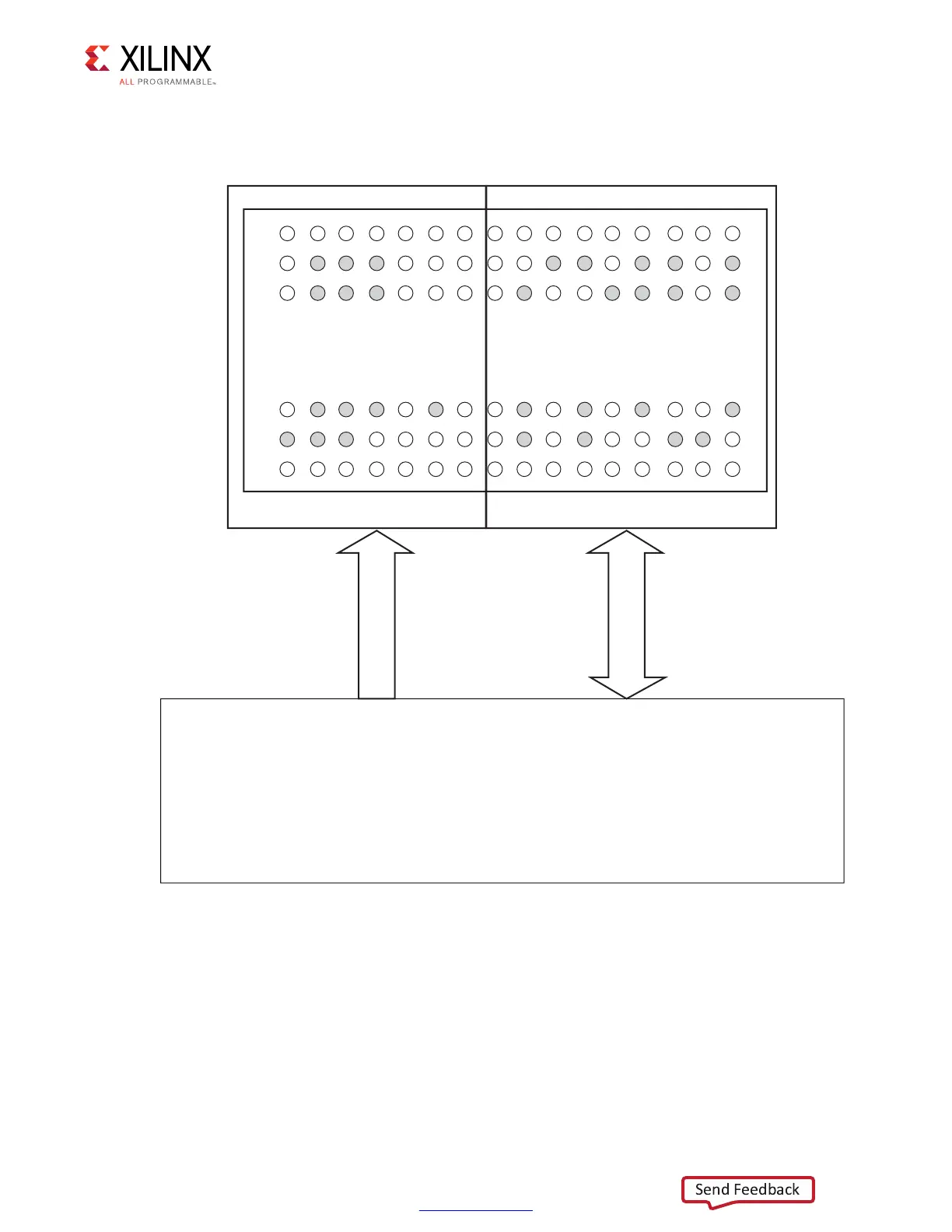

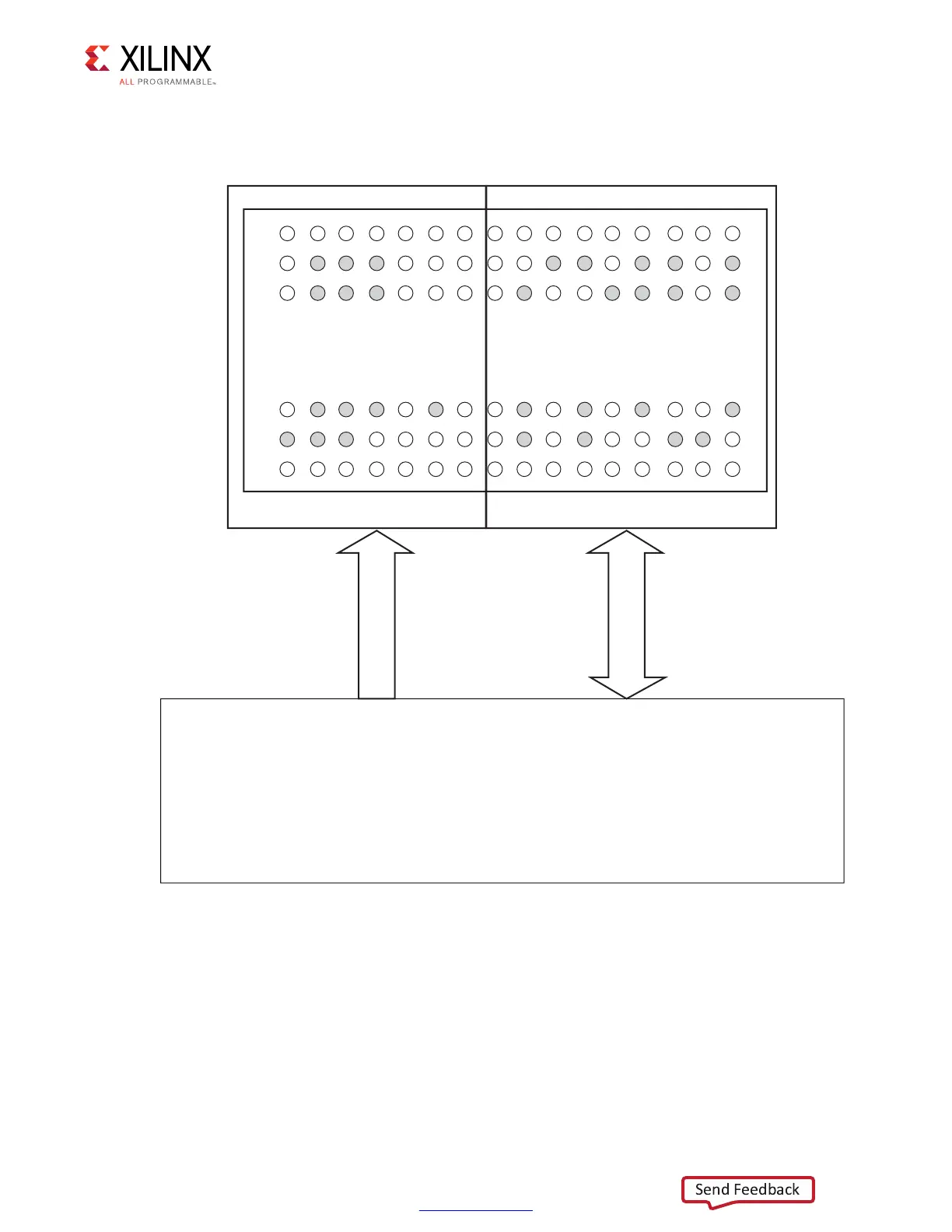

13. To optimize the signal routing, the recommendation for one component placement is

shown in Figure A-7.

X-Ref Target - Figure A-7

Figure A-7: Component Placement Recommendations for One Component

V

5

5

RESETA13

V

DD

A7A9

V

55A5A1

V

AEDQ

V

000

DQ4

V

A55Q

DQ6LDQ5#

V

DDQ

DQ2LDQ5

V

55

V

55Q

DQ0

V

550

DQQUDM

V

D0Q

DQ11DQ9

V

550

V

DD

V

55

V

000

DQ13DQ15

V

DD

A3A0

V

55

BA0BA2

NCCS#WE#

ODT

V

DDCAS#

NIC

V

55

RAS#

A14A8

V

5

5

A11A6

V

00

A1A4

V

5

5

DQ7DQ5

V

00Q

V

DD

V

5

5

V

5

5Q

V

DDQ

V

55Q

V

00

Q

LDM

V

55Q

DQ0

DQ8

V

55Q

V

00

UDQSDQ10

V

000

UDQS#DQ14

V

5

5Q

DQ12

V

00Q

V

5

55

A12BC#BA1

V

00

NC

V

REFCA

V

5

5

A10APZQNC

CK#

V

DDCKE

CK

V

5

5

NC

cmd/addr/ctrl

FPGA

cmd/addr/ctrl routing channel dq routing channel

dq

UG583_c2_18_073014

Loading...

Loading...