Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 178

UG586 November 30, 2016

www.xilinx.com

Chapter 1: DDR3 and DDR2 SDRAM Memory Interface Solution

IMPORTANT: Bits[31:27, 24:23, 14:12, and 7:3] in Table 1-58, page 136 are not used in this example.

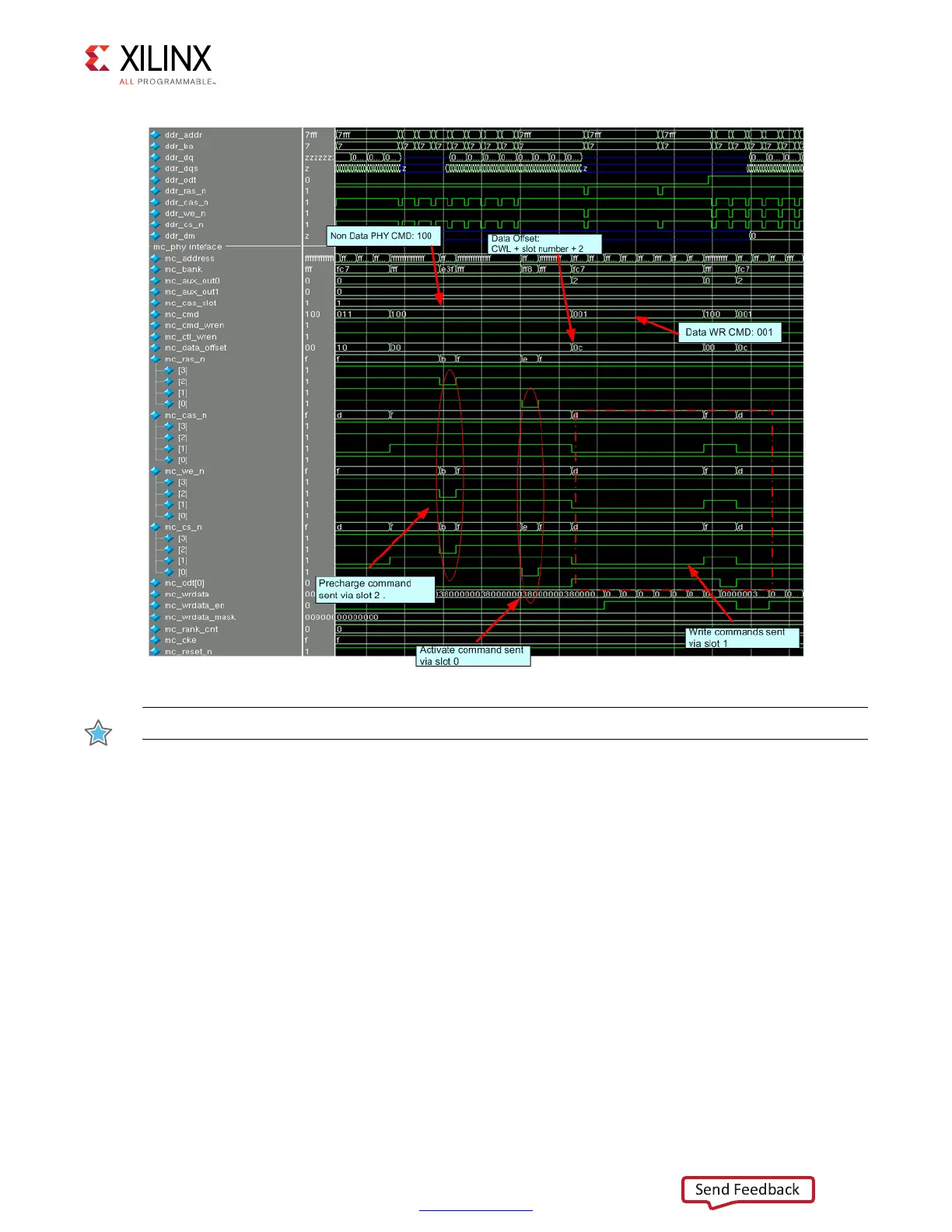

The write waveform shown in Figure 1-90 illustrates an example with calibrated PHY read

data offset = 10. For a selected slot number of 1, nCK_PER_CLK of 4, the read data offset is:

Read data offset = Calibrated PHY read data offset + slot number

= 10 + 1 = 11

X-Ref Target - Figure 1-89

Figure 1-89: Sending Write Commands in the PHY Interface (CWL = 9)

Loading...

Loading...