Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 520

UG586 November 30, 2016

www.xilinx.com

Chapter 4: LPDDR2 SDRAM Memory Interface Solution

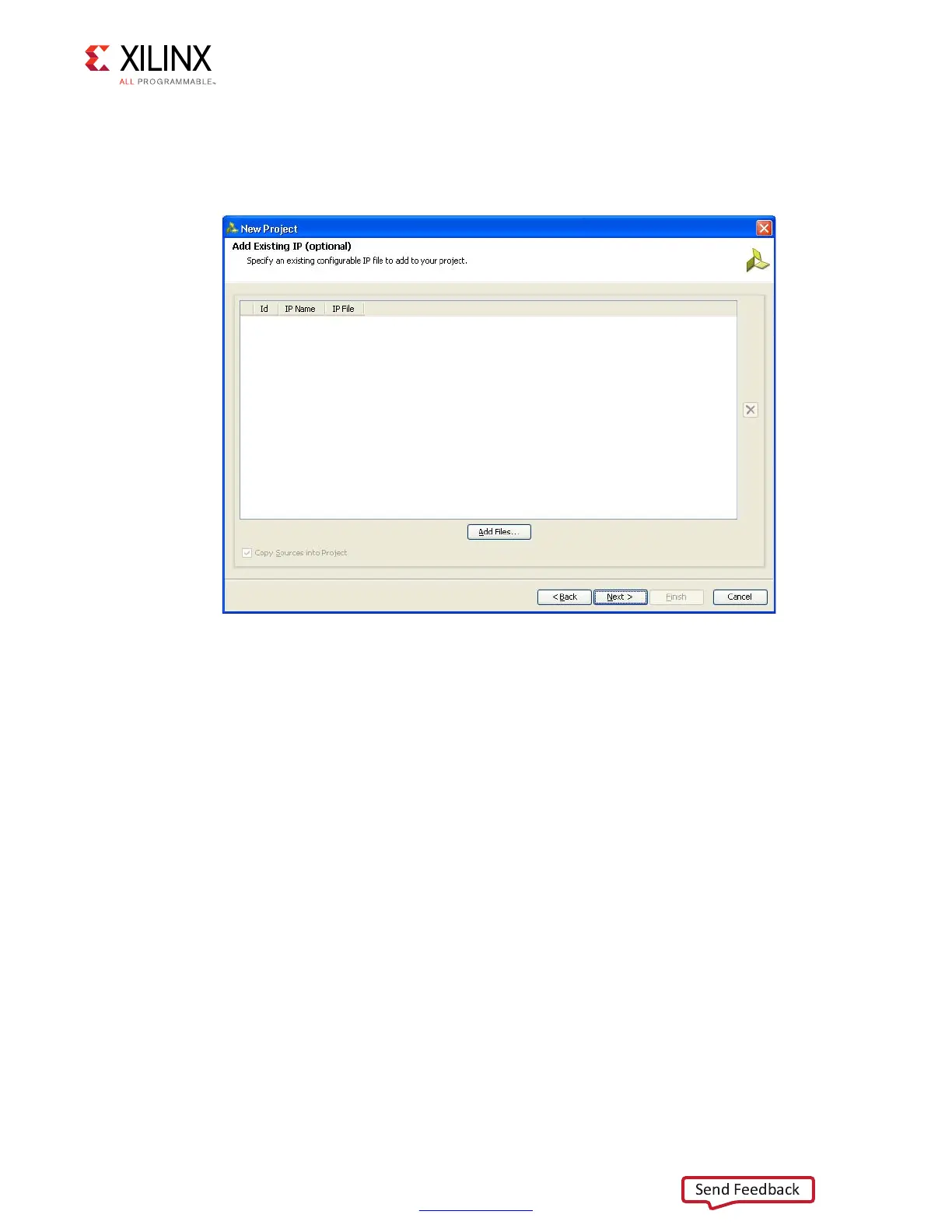

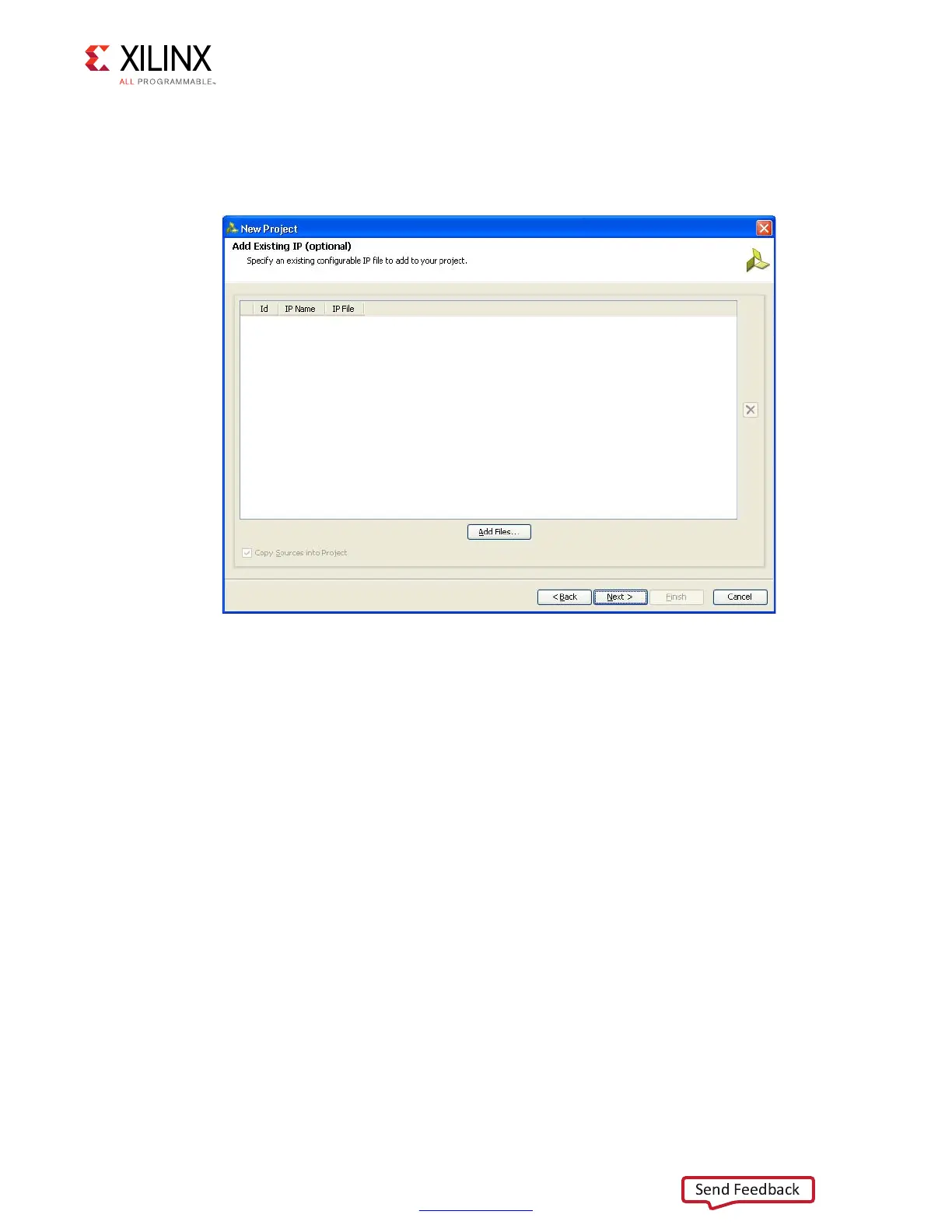

6. Click Next to open the Add Existing IP (Optional) page (Figure 4-6). If the IP is already

created, the XCI file generated by the IP can be added to the project and the previous

created IP files are automatically added to the project. If the IP was not created earlier,

proceed to the next page.

7. Click Next to open the Add Constraints (Optional) page (Figure 4-7). If the constraints

file exists in the repository, it can be added to the project. Proceed to the next page if

the constraints file does not exist.

X-Ref Target - Figure 4-6

Figure 4-6: Add Existing IP (Optional)

Loading...

Loading...