Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 431

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

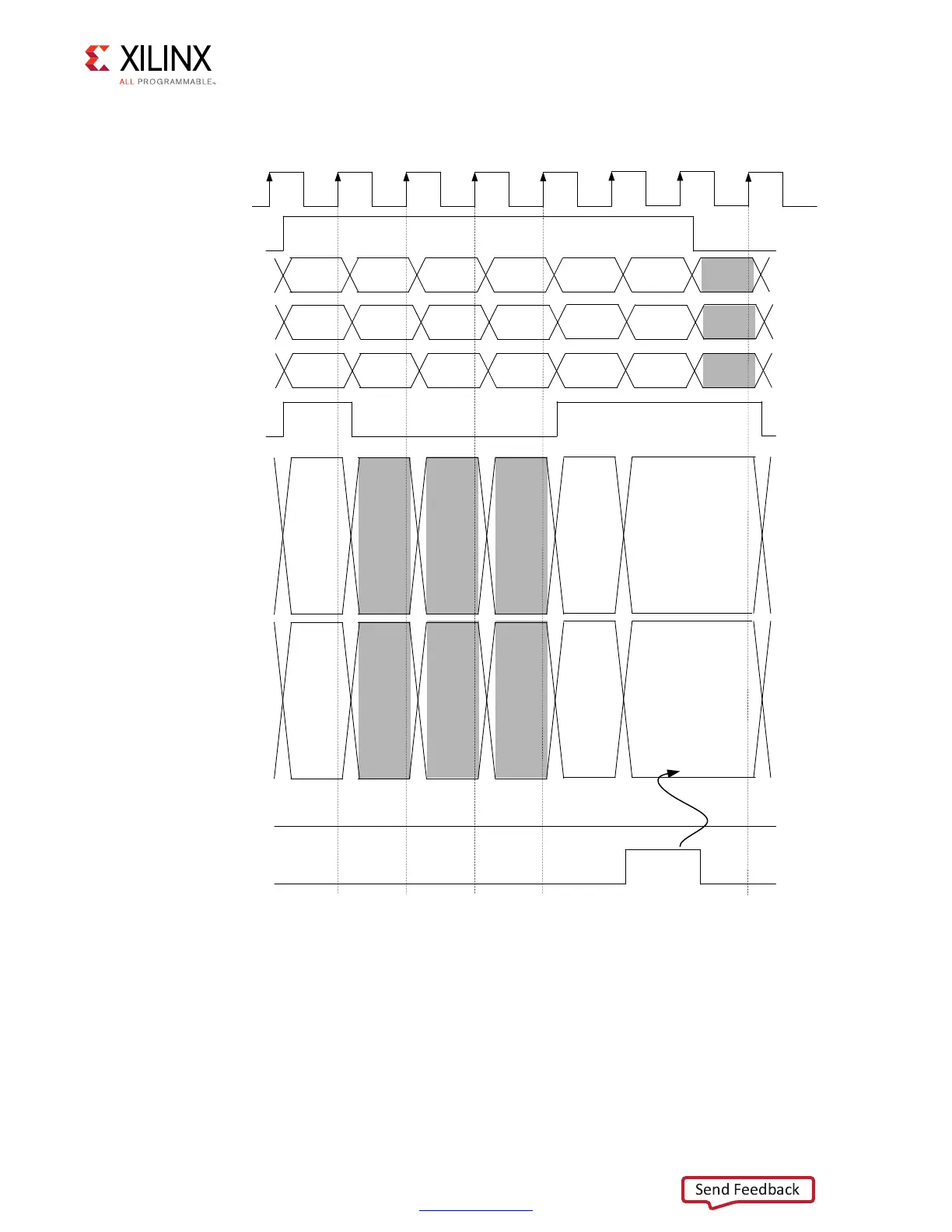

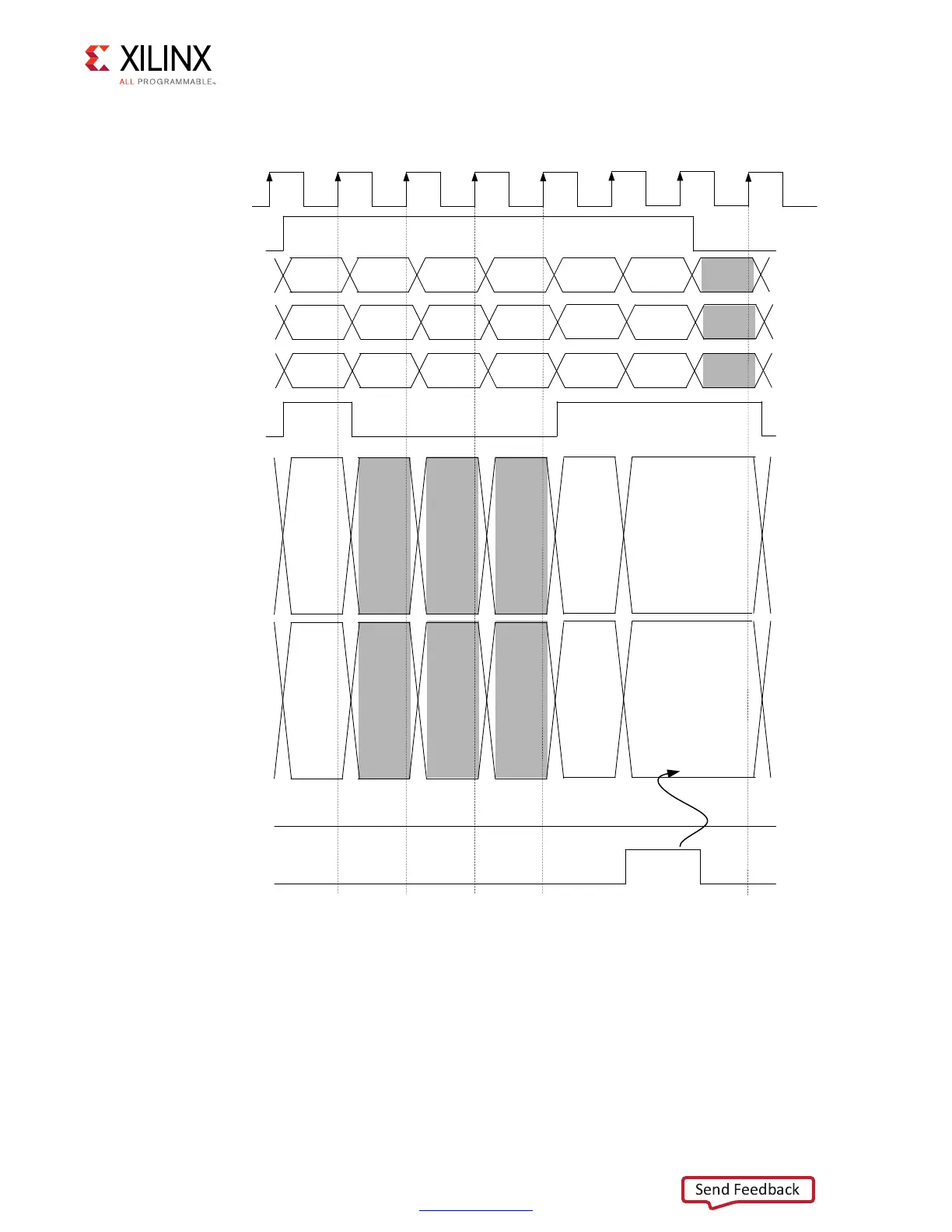

The client interface protocol for the RLDRAM 3 four-word burst architecture is shown in

Figure 3-41.

Before any requests can be accepted, the ui_clk_sync_rst signal must be deasserted

Low. After the ui_clk_sync_rst signal is deasserted, the user interface FIFOs can accept

commands and data for storage. The init_calib_complete signal is asserted after the

memory initialization procedure and PHY calibration are complete, and the core can begin

to service client requests.

X-Ref Target - Figure 3-41

Figure 3-41: RLDRAM 3 Client Interface Protocol (Four-Word Burst Architecture)

#,+

USER?WR?EN

[!!] [!!]

USER?ADDR

[READ

READ]

USER?CMD

[READ

./0]

[WRITE

WRITE]

[WRITE

./0]

[./0

!]

[!

./0]

["!

"!]

USER?BA

USER?WR?DM

USER?CMD?EN

[./0

READ]

[!

./0]

[./0

WRITE]

["!

"!]

[./0

"!]

["!

./0]

["!

./0]

USER?WR?DATA

[FALL

RISE

FALL

RISE

FALL

RISE

FALL

RISE]

[./0

!]

[./0

!]

USER?AFIFO?FULL

USER?WDFIFO?FULL

8

[FALL

RISE

FALL

RISE

FALL

RISE

FALL

RISE]

[FALL

RISE

FALL

RISE

./0

./0

./0

./0]

[FALL

RISE

FALL

RISE

./0

./0

./0

./0]

[./0

./0

./0

./0

FALL

RISE

FALL

RISE]

[./0

./0

./0

./0

FALL

RISE

FALL

RISE]

[./0

./0

./0

./0

FALL

RISE

FALL

RISE]

[./0

./0

./0

./0

FALL

RISE

FALL

RISE]

Loading...

Loading...