Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 432

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

A command request is issued by asserting user_cmd_en as a single cycle pulse. At this

time, the user_cmd, user_addr, and user_ba signals must be valid. To issue a read

request, user_cmd is set to 2’b01, while for a write request, user_cmd is set to 2'b00. For

a write request, the data is to be issued in the same cycle as the command by asserting the

user_wr_en signal High and presenting valid data on user_wr_data and user_wr_dm.

IMPORTANT: Both write and read commands in the same user_cmd cycle is not allowed.

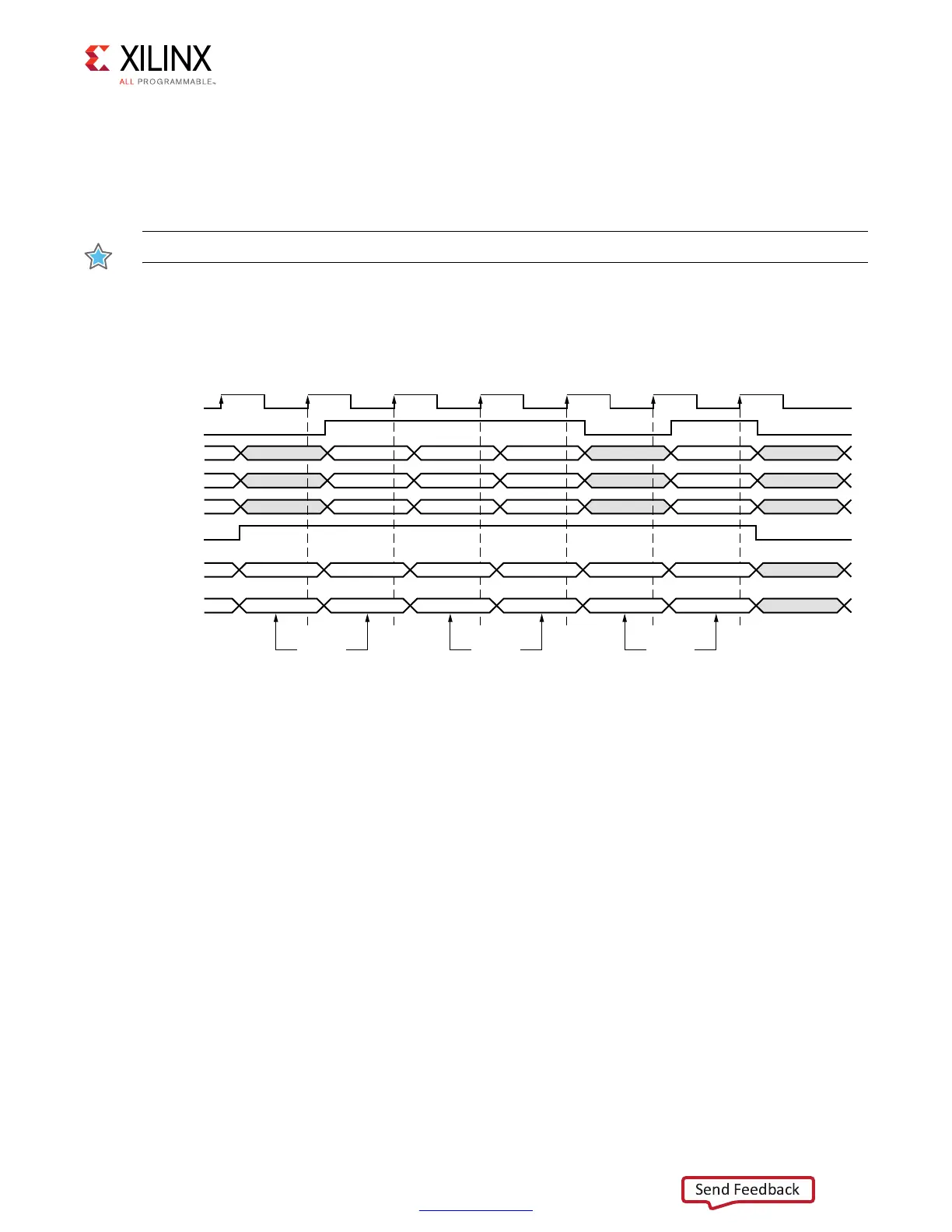

For RLDRAM II and eight-word burst architecture, an extra cycle of data is required for a

given write command, as shown in Figure 3-42. Any gaps in the command flow required can

be filled with read commands, if desired.

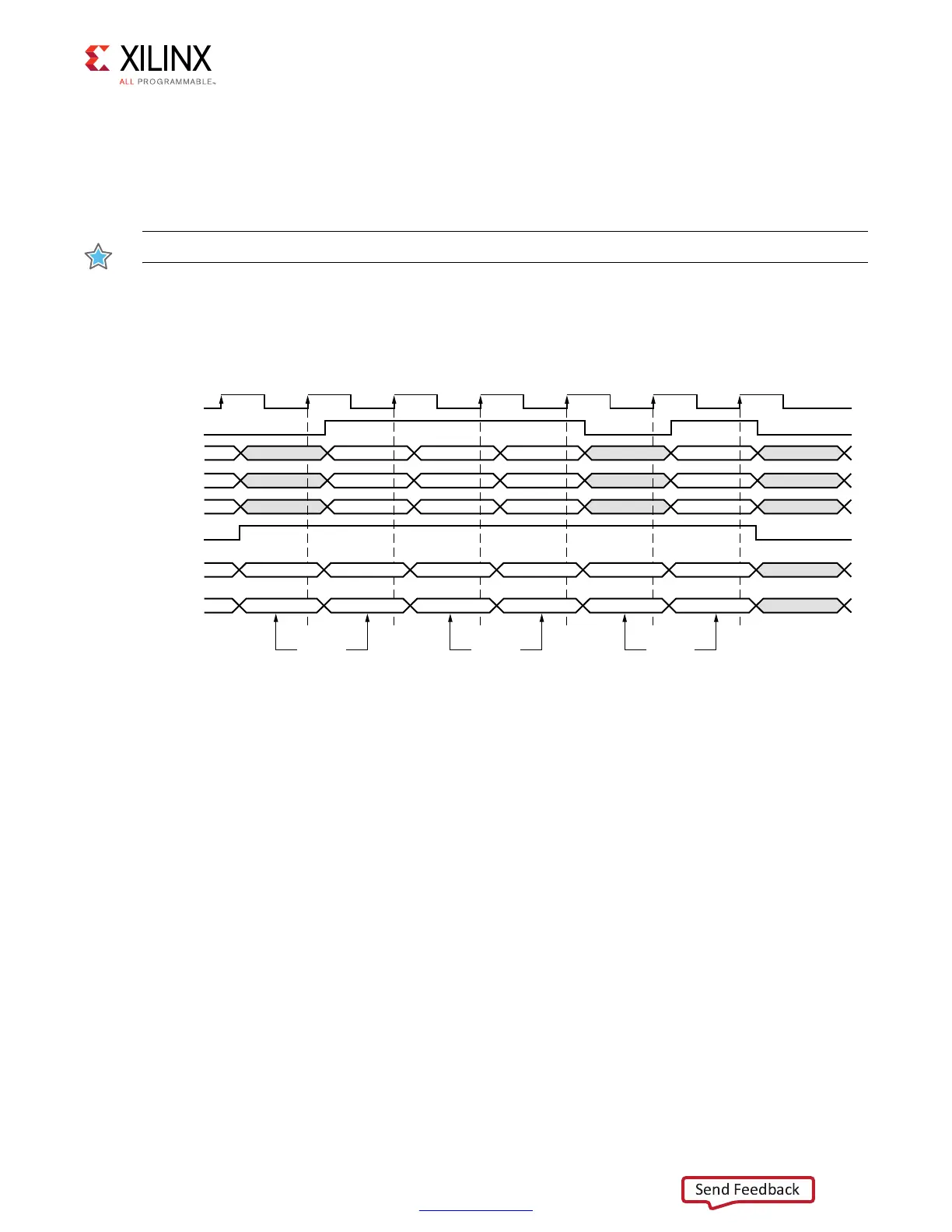

The client interface protocol for the RLDRAM 3 eight-word burst architecture is shown in

Figure 3-43.

X-Ref Target - Figure 3-42

Figure 3-42: RLDRAM II Client Interface Protocol (Eight-Word Burst Architecture)

"! "! "! "!

USER?CMD?EN

USER?CMD

USER?ADDR

USER?BA

USER?WR?EN

USER?WR?DATA

USER?WR?DM

#,+

5'?C??

! ! ! !

[FALLRISEFALLRISE] [FALLRISEFALLRISE] [FALLRISEFALLRISE] [FALLRISEFALLRISE] [FALLRISEFALLRISE]

[FALLRISEFALLRISE]

$ATAFOR

RD7RITE

$ATAFOR

ND7RITE

$ATAFOR

ST7RITE

ST7RITE 2EAD ND7RITE RD7RITE

[FALLRISEFALLRISE] [FALLRISEFALLRISE] [FALLRISEFALLRISE] [FALLRISEFALLRISE] [FALLRISEFALLRISE]

[FALLRISEFALLRISE]

Loading...

Loading...