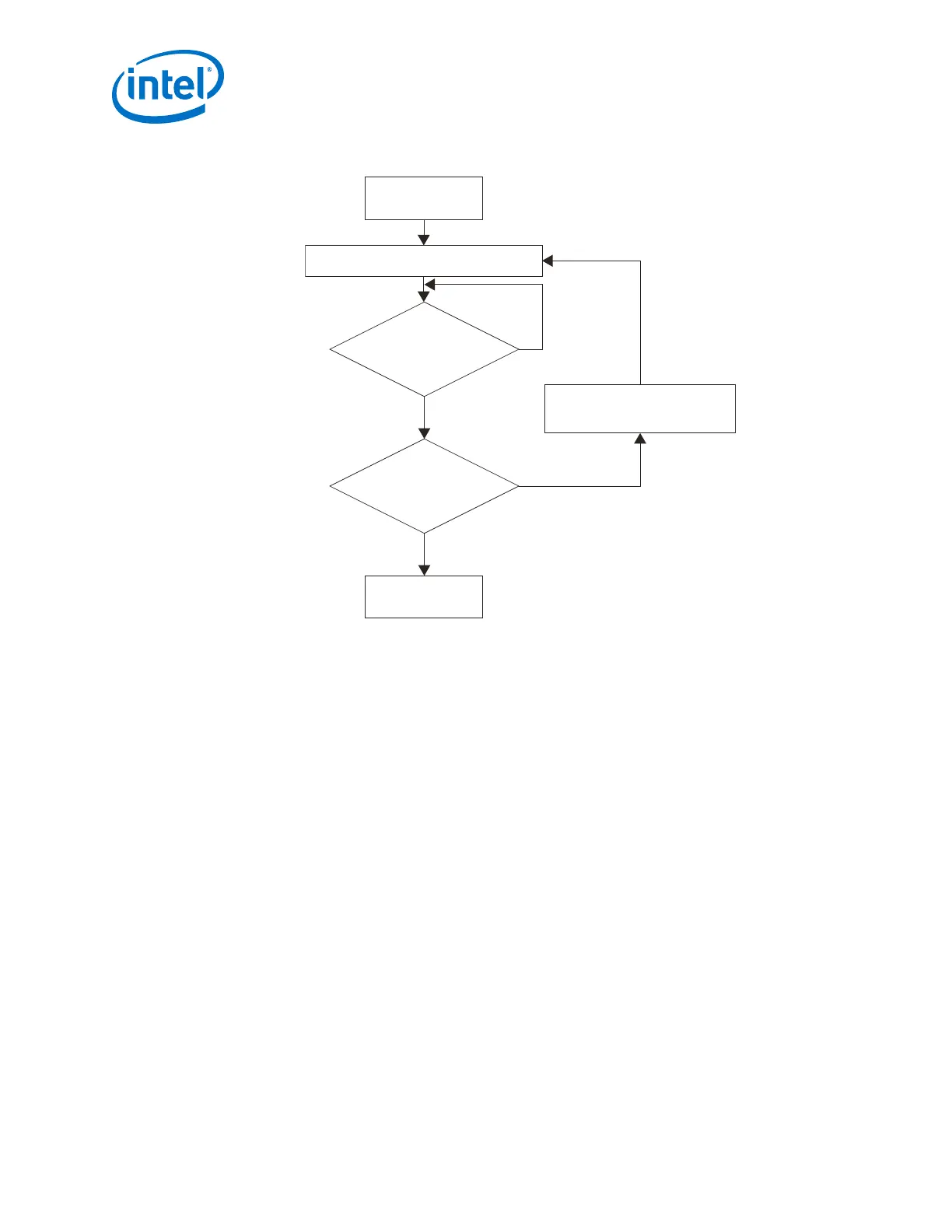

Figure 36. State Flow of the RX FIFO Deskew

Exit from

rx_digitalreset

Deassert all Lane’s rx_enh_fifo_rd_en

All Lane’s

rx_enh_fifo_pempty

Deasserted?

yes

All Lane’s

rx_enh_fifo_pfull

Deasserted?

yes

Assert rx_enh_fifo_align_clr for at

least 4 rx_coreclkin Cycles

no

no

RX FIFO Deskew

Completed

Each lane's rx_enh_fifo_rd_en should remain deasserted before the RX FIFO

deskew is completed. After frame lock is achieved (indicated by the assertion of

rx_enh_frame_lock; this signal is not shown in the above state flow), data is

written into the RX FIFO after the first alignment word (SYNC word) is found on that

channel. Accordingly, the RX FIFO partially empty flag (rx_enh_fifo_pempty) of

that channel is asserted. The state machine monitors the rx_enh_fifo_pempty and

rx_enh_fifo_pfull signals of all channels. If the rx_enh_fifo_pempty signals

from all channels deassert before any channels rx_enh_fifo_pfull assert, which

implies the SYNC word has been found on all lanes of the link, the MAC layer can start

reading from all the RX FIFO by asserting rx_enh_fifo_rd_en simultaneously.

Otherwise, if the rx_enh_fifo_pfull signal of any channel asserts high before the

rx_enh_fifo_pempty signals deassertion on all channels, the state machine needs

to flush the RX FIFO by asserting rx_enh_fifo_align_clr high for 4 cycles and

repeating the soft deskew process.

The following figure shows one RX deskew scenario. In this scenario, all of the RX

FIFO partially empty lanes are deasserted while the pfull lanes are still deasserted.

This indicates the deskew is successful and the FPGA fabric starts reading data from

the RX FIFO.

2. Implementing Protocols in Arria 10 Transceivers

UG-01143 | 2018.06.15

Intel

®

Arria

®

10 Transceiver PHY User Guide

102

Loading...

Loading...